# phyCORE-MCF548x

Hardware Manual

**Edition January 2005**

A product of a PHYTEC Technology Holding company

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark ( $^{TM}$ ) and copyright (©) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC Messtechnik GmbH assumes no responsibility for any inaccuracies. PHYTEC Messtechnik GmbH neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC Messtechnik GmbH reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages which might result.

Additionally, PHYTEC Messtechnik GmbH offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC Messtechnik GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2005 PHYTEC Messtechnik GmbH, D-55129 Mainz.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC Messtechnik GmbH.

|                          | EUROPE                                                                           | NORTH AMERICA                                                                              |

|--------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Address:                 | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>USA |

| Ordering<br>Information: | +49 (800) 0749832<br>order@phytec.de                                             | 1 (800) 278-9913<br>sales@phytec.com                                                       |

| Technical<br>Support:    | +49 (6131) 9221-31<br>support@phytec.de                                          | 1 (800) 278-9913<br>support@phytec.com                                                     |

| Fax:                     | +49 (6131) 9221-33                                                               | 1 (206) 780-9135                                                                           |

| Web Site:                | http://www.phytec.de                                                             | http://www.phytec.com                                                                      |

1<sup>st</sup> Edition: January 2005

| Pref | ace   |                                                     | 1  |

|------|-------|-----------------------------------------------------|----|

| 1    | Intro | oduction                                            | 3  |

|      | 1.1   | Block Diagram                                       | 6  |

|      | 1.2   | View of the phyCORE-MCF548x                         | 7  |

|      | 1.3   | Minimum Requirements to Operate the phyCORE-MCF548x | 8  |

| 2    | Pin l | Description                                         | 9  |

| 3    | Jum   | pers                                                | 23 |

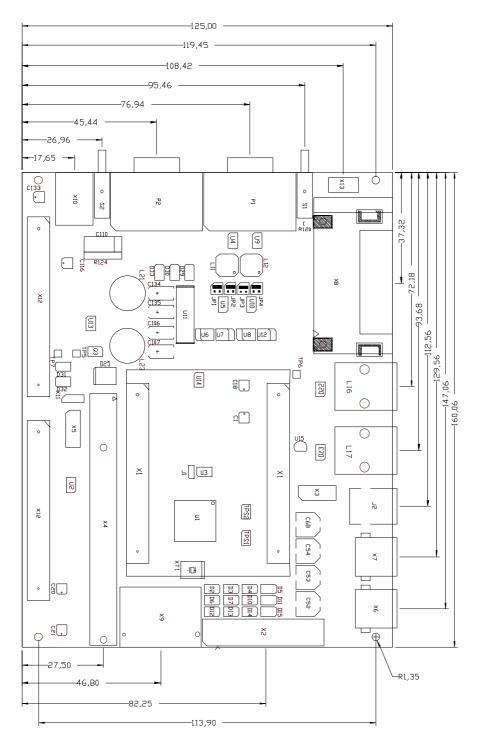

| 4    | Pow   | er Requirements                                     | 33 |

|      | 4.1   | Voltage Supervision and Reset                       | 35 |

| 5    | Syst  | em Start-Up Configuration                           | 37 |

| 6    | Syst  | em Memory                                           | 39 |

|      | 6.1   | Flash Memory                                        | 40 |

|      | 6.2   | DDR SDRAM                                           | -  |

|      | 6.3   | Serial Memory                                       |    |

| 7    | XPL   | D System Logic Device                               |    |

|      | 7.1   | XPLD Firmware Development                           |    |

| 8    | Seria | al Interfaces                                       |    |

|      | 8.1   | RS-232 Interface                                    |    |

|      | 8.2   | CAN Interface                                       |    |

|      | 8.3   | BDM Debug Interface                                 |    |

|      | 8.4   | Ethernet Interface                                  |    |

|      |       | 8.4.1 PHY Physical Layer Transceiver                |    |

|      |       | 8.4.2 MAC Address                                   | 56 |

|      | 8.5   | USB 2.0 Interface                                   |    |

| 9    |       | I-Time Clock RTC-8564 (U16)                         |    |

| 10   |       | CORE Development Board PCM-982                      |    |

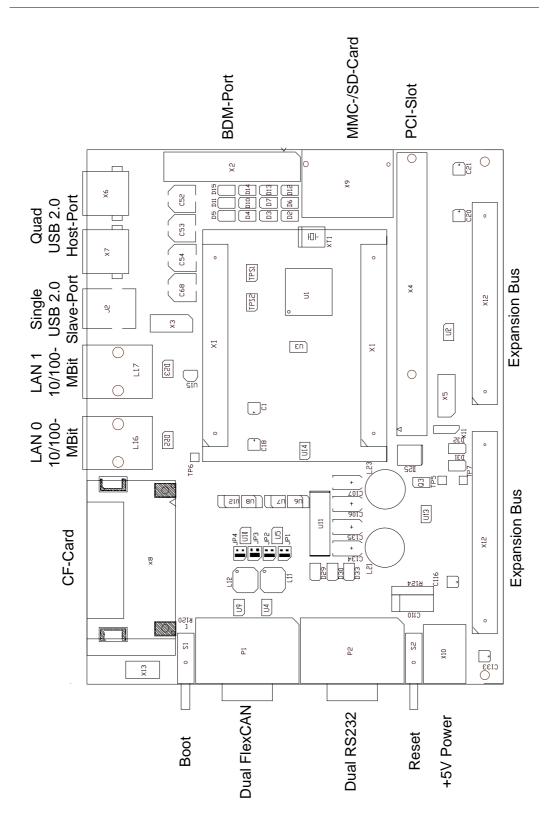

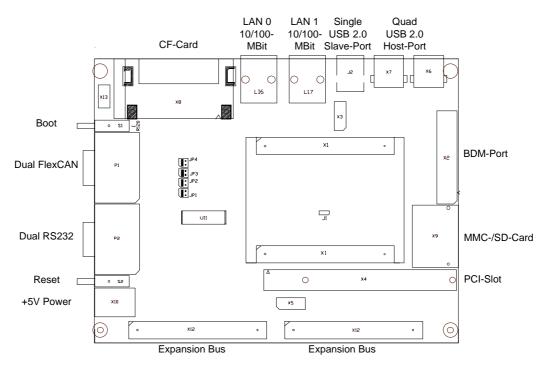

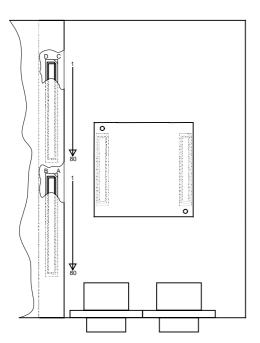

|      |       | Concept of the phyCORE Development Board PCM-982    |    |

|      | 10.2  | Development Board PCM-982 Overview                  |    |

|      |       | 10.2.1 Connectors, Buttons, LEDs                    | 60 |

|      |       | 10.2.2 Jumpers on the phyCORE Development Board     | -  |

|      |       | PCM-982                                             | 63 |

|      | 10.3  | Functional Components on the phyCORE Development    |    |

|      |       | Board PCM-982                                       |    |

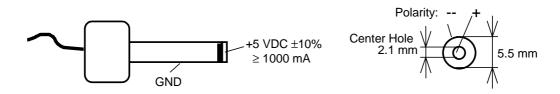

|      |       | 10.3.1 Power Supply at X10                          |    |

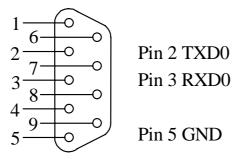

|      |       | 10.3.2 First Serial Interface at Socket P2A         |    |

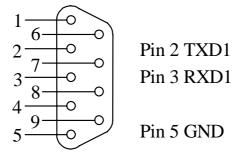

|      |       | 10.3.3 Second Serial Interface at Socket P2B        |    |

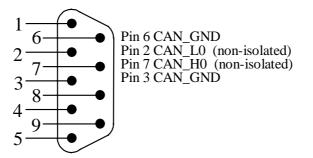

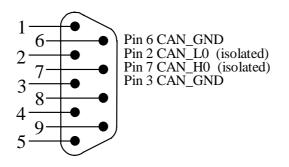

|      |       | 10.3.4 First CAN Interface at Plug P1A              | 67 |

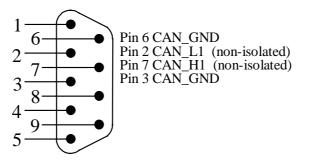

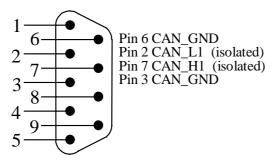

| 10.3.6Programmable LED D29                                                                                                                                                                                                                                                                                               |      | 10.3.5 | Second CAN Interface at Plug P1B | 69 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|----------------------------------|----|

| 10.3.7Pin Assignment Summary of the phyCORE, the<br>Expansion Bus and the Patch Field                                                                                                                                                                                                                                    |      |        | C C                              |    |

| Expansion Bus and the Patch Field                                                                                                                                                                                                                                                                                        |      |        | -                                |    |

| 10.3.8Silicon Serial Number/Temperature Sensor                                                                                                                                                                                                                                                                           |      |        |                                  | 71 |

| 10.3.9 BDM Port X28110.3.10 Technical Specification of the Development Board8210.3.11 Release Notes8411 Technical Specifications of the phyCORE-MCF548x8512 Hints for Handling the Module8813 Design Considerations - Check List8914 Revision History9015 Component Placement Diagram91A Appendices93A.1 Release Notes93 |      | 10.3.8 |                                  |    |

| 10.3.10 Technical Specification of the Development Board82<br>10.3.11 Release Notes                                                                                                                                                                                                                                      |      |        | <b>A</b>                         |    |

| 10.3.11 Release Notes8411 Technical Specifications of the phyCORE-MCF548x8512 Hints for Handling the Module8813 Design Considerations - Check List8914 Revision History9015 Component Placement Diagram91A Appendices93A.1 Release Notes93                                                                               |      |        |                                  |    |

| 11Technical Specifications of the phyCORE-MCF548x8512Hints for Handling the Module8813Design Considerations - Check List8914Revision History9015Component Placement Diagram91AAppendices93A.1Release Notes93                                                                                                             |      |        |                                  |    |

| 12Hints for Handling the Module                                                                                                                                                                                                                                                                                          | 11   |        |                                  |    |

| 13Design Considerations - Check List                                                                                                                                                                                                                                                                                     | 12   | -      | L V                              |    |

| 14Revision History9015Component Placement Diagram91AAppendices93A.1Release Notes93                                                                                                                                                                                                                                       |      |        | -                                |    |

| 15Component Placement Diagram91AAppendices93A.1Release Notes93                                                                                                                                                                                                                                                           | -    | 0      |                                  |    |

| A Appendices                                                                                                                                                                                                                                                                                                             | 15   |        |                                  |    |

| A.1 Release Notes                                                                                                                                                                                                                                                                                                        |      |        |                                  |    |

|                                                                                                                                                                                                                                                                                                                          |      |        |                                  |    |

|                                                                                                                                                                                                                                                                                                                          | Inde |        |                                  |    |

## **Index of Figures**

| Figure 1:  | Block Diagram phyCORE-MCF548x6                                                                        |

|------------|-------------------------------------------------------------------------------------------------------|

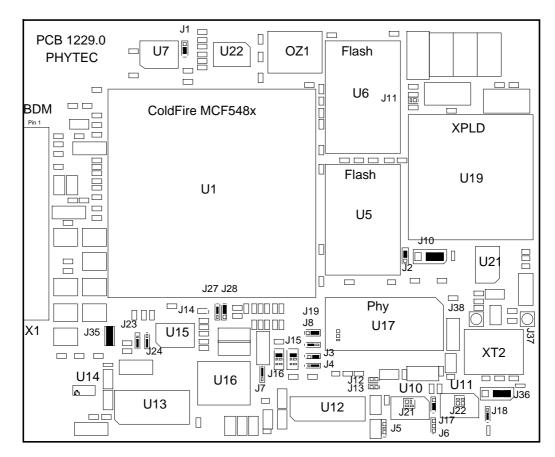

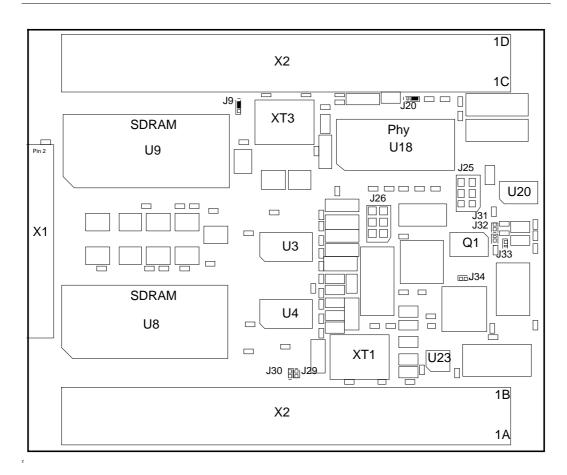

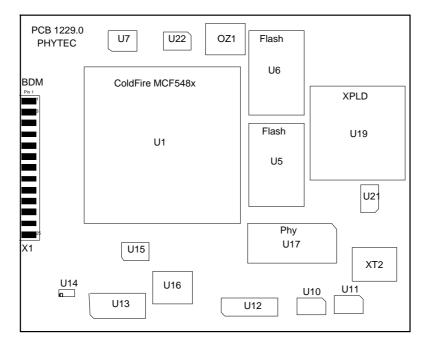

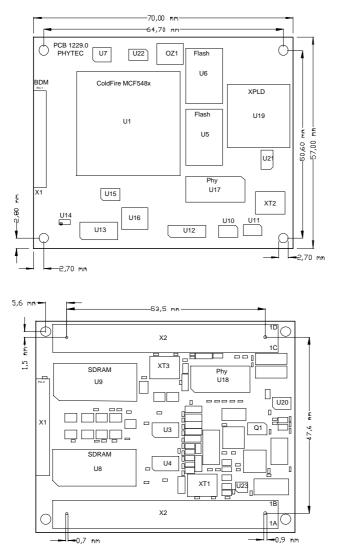

| Figure 2:  | View of the phyCORE-MCF548x Revision 1229.0 (M 1.5:1) 7                                               |

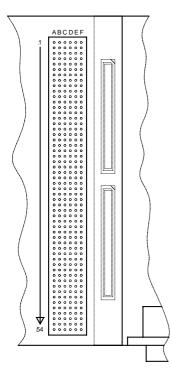

| Figure 3:  | Pinout of the phyCORE-MCF548x (Bottom View)9                                                          |

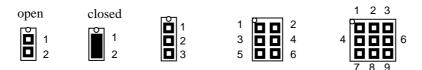

| Figure 4:  | Numbering of the Jumper Pads23                                                                        |

| Figure 5:  | Location of the Jumpers (Controller Side)and Default<br>Settings (phyCORE-MCF548x Standard Version)23 |

| Figure 6:  | Location of the Jumpers (Connector Side) and Default<br>Settings (phyCORE-MCF548x Standard Version)24 |

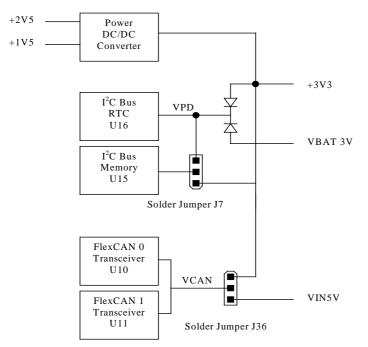

| Figure 7:  | Power Supply Diagram                                                                                  |

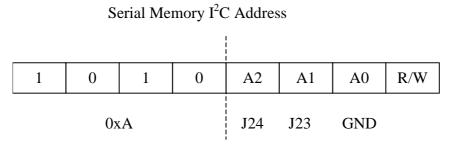

| Figure 8:  | Serial Memory I <sup>2</sup> C Slave Address45                                                        |

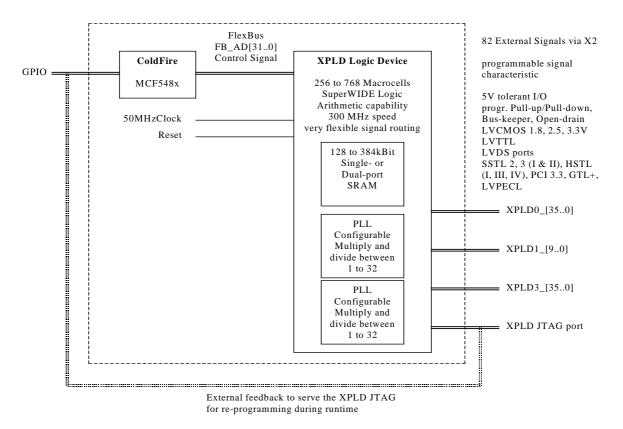

| Figure 9:  | XPLD Configuration                                                                                    |

| Figure 10: | BDM Interface Card Edge Header X1 (Top View)52                                                        |

| Figure 11: | View of the Development Board PCM-982                                                                 |

| Figure 12: | Numbering of Jumper Pads                                                                              |

| Figure 13: | Location of the Jumpers (View of the Component Side)63                                                |

| Figure 14: | Connecting the Supply Voltage at X1065                                                                |

| Figure 15: | Pin Assignment of the DB-9 Socket P2A as First RS-232<br>(Front View)                                 |

| Figure 16: | Pin Assignment of the DB-9 Socket P2B as Second RS-232<br>(Front View)                                |

| Figure 17: | Pin Assignment of the DB-9 Plug P1A (CAN Transceiver on phyCORE-MCF548x, Front View)                  |

| Figure 18: | Pin Assignment of the DB-9 Plug P1A (CAN Transceiver on Development Board with Galvanic Separation)   |

| Figure 19: | Pin Assignment of the DB-9 Plug P1B (CAN Transceiver on phyCORE-MCF548x, Front View)                  |

| Figure 20: | Pin Assignment of the DB-9 Plug P2B (CAN Transceiver on Development Board with Galvanic Separation)70 |

| Figure 21: | Pin Assignment Scheme of the Expansion Bus72                                                          |

| Figure 22: | Pin Assignment Scheme of the Patch Field72                                                            |

|            |                                                                                                       |

## phyCORE-MCF548x

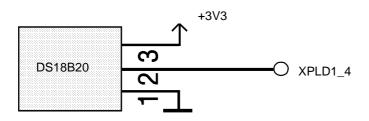

| Figure 23: Connecting the DS18B20 Temperature Sensor with Silicon<br>Serial Number | 80 |

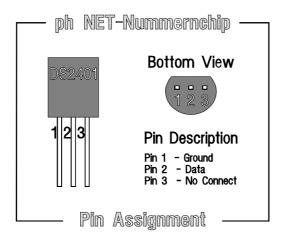

|------------------------------------------------------------------------------------|----|

| Figure 24: Pin Assignment of the DS2401 Silicon Serial Number                      | 80 |

| Figure 25 Physical Dimensions of the Development Board PCM-982                     | 82 |

| Figure 26: Physical Dimensions                                                     | 85 |

| Figure 27: phyCORE-MCF548x Component Placement, Top View                           | 91 |

| Figure 28: phyCORE-MCF548x Component Placement, Bottom View                        | 91 |

## **Index of Tables**

| Table 1:  | Pinout of the phyCORE-Connector X2                                                                                      | .21  |

|-----------|-------------------------------------------------------------------------------------------------------------------------|------|

| Table 2:  | Jumper Settings                                                                                                         | . 31 |

| Table 3:  | System Start-up Configuration                                                                                           | . 37 |

| Table 4:  | System Start-up Configuration Test/Debug Port                                                                           | . 38 |

| Table 5:  | Choice of Flash Memory Devices and Manufacturers                                                                        | .40  |

| Table 6:  | DDR SDRAM Device Selection                                                                                              | .43  |

| Table 7:  | Serial Memory Options for U15                                                                                           | . 44 |

| Table 8:  | Serial Memory I <sup>2</sup> C Address (Examples)                                                                       | .45  |

| Table 9:  | 26-Pin BDM Connector (X1) and Corresponding Pins on the phyCORE-Connector (X2)                                          | . 53 |

| Table 10: | Signal Definition PHY 0 Ethernet Port (U17)                                                                             | . 55 |

| Table 11: | Signal Definition PHY 1 Ethernet Port (U18)                                                                             | . 55 |

| Table 12: | Signal Definition USB 2.0 Port                                                                                          | . 56 |

| Table 13: | Development Board Jumper Overview                                                                                       | . 64 |

| Table 14: | Jumper Configuration for CAN Plug P1A Using the CAN<br>Transceiver on the phyCORE-MCF548x                               | . 67 |

| Table 15: | Jumper Configuration for CAN Plug P1A Using the CAN<br>Transceiver on the Development Board with Galvanic<br>Separation | . 68 |

| Table 16: | Jumper Configuration for CAN Plug P2B Using the CAN<br>Transceiver on the phyCORE-MCF548x                               |      |

| Table 17: | Jumper Configuration for CAN Plug P2B using the CAN<br>Transceiver on the Development Board with Galvanic<br>Separation | .70 |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|

| Table 18: | Signal Pin Assignment for the phyCORE-MCF548x /<br>Development Board / Expansion Board                                  | .78 |

| Table 19: | Pin Assignment Power Supply for the phyCORE-MCF548x /<br>Development Board / Expansion Board                            |     |

| Table 20: | Pin Assignment of the BDM Pin Header X2                                                                                 | .81 |

| Table 21: | Technical Data of the Development Board PCM-982                                                                         | .83 |

| Table 22: | Technical Data of the phyCORE-MCF548x                                                                                   | .86 |

### Preface

This phyCORE-MCF548x Hardware Manual describes the board's design and functions. Precise specifications for the Freescale MCF548X microcontroller series can be found in the enclosed MCF548X microcontroller Data Sheet/User's Manual. If software is included please also refer to additional documentation for this software.

In this hardware manual and in the attached schematics, low active signals are denoted by a "/" in front of the signal name (i.e.: /RD). A "0" indicates a logic-zero or low-level signal, while a "1" represents a logic-one or high-level signal. The MSB and LSB of the data and address busses shown in the circuit diagram are based on the conventions of Freescale. Accordingly, D0 and A0 represent the LSB, while D31 and A31 represent the MSB. These conventions are also valid for the parallel I/O signals.

## Declaration regarding Electro Magnetic Conformity of the PHYTEC phyCORE-MCF548x

PHYTEC Single Board Computers (henceforth products) are designed for installation in electrical appliances or as dedicated Evaluation Boards (i.e.: for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### Note:

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m. PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header rows or connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

The phyCORE-MCF548x is one of a series of PHYTEC Single Board Computers that can be populated with different controllers and, hence, offers various functions and configurations. PHYTEC supports common 8-, 16- and selected 32-bit controllers on two types of Single Boards Computers:

- (1) as the basis for Rapid Development Kits which serve as a reference and evaluation platform

- (2) as insert-ready, fully functional micro-, mini- and phyCORE OEM modules, which can be embedded directly into the user's peripheral hardware, design.

PHYTEC's microcontroller modules allow engineers to shorten development horizons, reduce design costs and speed project concepts from design to market.

## **1** Introduction

The phyCORE-MCF548x belongs to PHYTEC's phyCORE Single Board Computer module family. The phyCORE SBCs represent the continuous development of PHYTEC Single Board Computer technology. Like its mini-, micro- and nanoMODUL predecessors, the phyCORE boards integrate all core elements of a microcontroller system on a sub-miniature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware developments.

As independent research indicates that approximately 70 % of all EMI (Electro Magnetic Interference) problems stem from insufficient supply voltage grounding of electronic components in high frequency environments the phyCORE board design features an increased pin package. The increased pin package allows dedication of approximately 20 % of all pin header connectors on the phyCORE boards to Ground. This improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI and EMC guidelines using phyCORE boards even in high noise environments.

phyCORE boards achieve their small size through modern SMD technology and multi-layer design. In accordance with the complexity of the module, 0402-packaged SMD and laser-drilled Microvias components are used on the boards, providing phyCORE users with access to this cutting edge miniaturization technology for integration into their own design.

The phyCORE-MCF548x is a subminiature (70 x 57 mm) insert-ready Single Board Computer populated with Freescale's ColdFire MCF548X microcontroller. Its universal design enables its insertion in a wide range of embedded applications. All controller signals and ports extend from the controller to high-density (0.635 mm) Molex pin header connectors aligning two sides of the board, allowing it to be plugged like a "big chip" into a target application. Precise specifications for the controller populating the board can be found in the applicable controller User's Manual or Data Sheet. The descriptions in this manual are based on the MCF548X controller. No description of compatible microcontroller derivative functions is included, as such functions are not relevant for the basic functioning of the phyCORE-MCF548x.

#### The phyCORE-MCF548x offers the following features:

- Single Board Computer in subminiature form factor (70 x 57 mm) according to phyCORE specifications

- all applicable controller and other logic signals extend to two high-density 160-pin Molex connectors

- processor: Freescale embedded ColdFire MCF548X (200 MHz clock)

#### **Internal Features of the MCF548X:**

- 32-bit ColdFire V4e core, 200 MHz CPU speed

- 32 kByte instruction cache

- 32 kByte data cache

- MMU with 32 entries

- 64-bit FPU double precision IEEE-754

- EMAC unit

- DMA unit

- Encryption unit

- 32 kByte SRAM

- Watchdog

- Two system timers

- Four 32-bit general purpose timers

- Four UARTs

- SPI interfaces

- Two CAN 2.0B interfaces

- I<sup>2</sup>C Maser/Slave controller

- Two Fast Ethernet controllers

- USB2.0 Slave

- PCI bus

- BDM test/debug port

#### **Memory Configuration**<sup>1</sup>:

- DDR SDRAM: 64 MByte to 128 MByte

- Flash: 32 MByte to 64 MByte Intel Strata Flash memory, 32-Bit memory width, synchronous (K3) or asynchronous (J3) devices are supported

- I<sup>2</sup>C Memory: 4 kByte EEPROM (up to 32 kByte, alternatively I<sup>2</sup>C FRAM, I<sup>2</sup>C SRAM)

#### **Other Board-Level Features:**

- Four UART ports RS-232 interfaces (RxD/TxD/RTS/CTS) and two TTL-level interfaces

- Two CAN ports, on-board CAN transceivers; also configurable as TTL

- Two 10/100Mbit Ethernet ports

- Logic Device Lattice ispXPLD 5000 family 256/512/768 Macrocells and 128/256/384 kBit SRAM, in-systemprogrammable For applications like: single-, dual-port RAM or FIFO Timer, PWM, CapComp etc. Decoder, Encoder IP core application-specific logic special bus interfaces multi-purpose I/O signals etc.

- PCI 2.2 bus

- SPI bus, Synchronous Serial Interface with two Chip Selects

- $I^2C$  bus

- I<sup>2</sup>C Real-Time Clock with calendar and alarm function

- 12-bit ADC, 8 channels, connected to  $I^2C$  Bus

- 12-bit DAC, 1 channel, connected to  $I^2C$  Bus

- JTAG/BDM test/debug port

- Industrial temperature range (-40...+85°C)

<sup>1:</sup> Please contact PHYTEC for more information about additional module configurations.

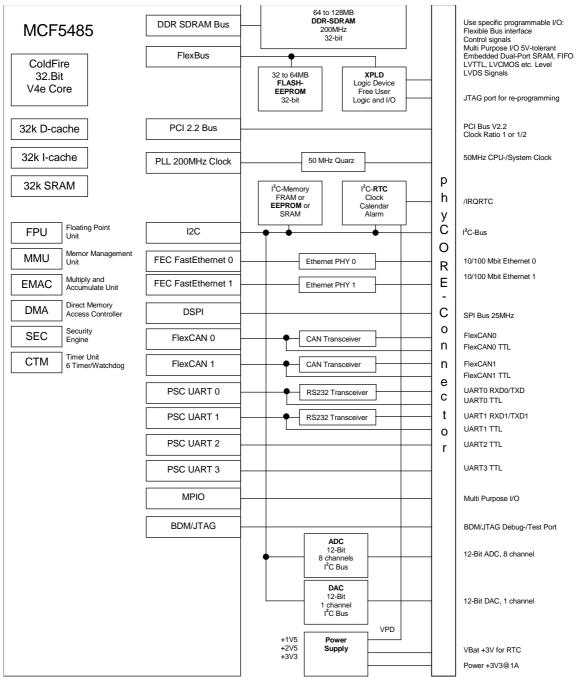

## 1.1 Block Diagram

*Figure 1: Block Diagram phyCORE-MCF548x*

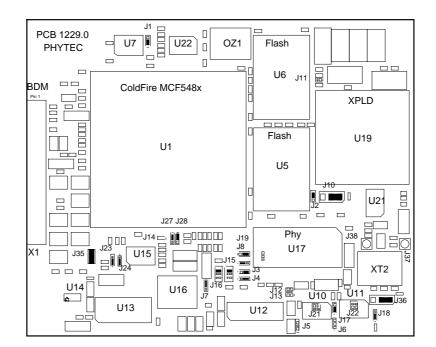

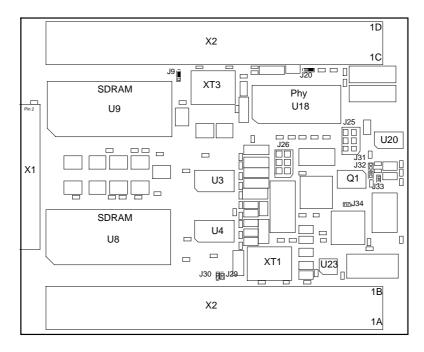

## 1.2 View of the phyCORE-MCF548x

*Figure 2:* View of the phyCORE-MCF548x Revision 1229.0 (M 1.5:1)

## 1.3 Minimum Requirements to Operate the phyCORE-MCF548x

Basic operation of the phyCORE-MCF548x only requires supply of a +3V3 input voltage and the corresponding GND connection.

These supply pins are located at the phyCORE-connector X2:

| +3V3 | X2 | 1C, 2C, 1D, 2D, 4D, 5D   |

|------|----|--------------------------|

| GND  | X2 | 3C, 3D, 7C, 9D, 12C, 14D |

#### **Caution:**

We recommend connecting all available +3V3 input pins to the power supply system on a custom carrier board housing the phyCORE-MCF548x and at least the matching number of GND pins neighboring the +3V3 pins.

In addition, proper implementation of the phyCORE module into a target application also requires connecting all GND pins neighboring signals that are being used in the application circuitry.

Please refer to section 4 for more information.

## 2 Pin Description

Please note that all module connections are not to exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller manuals/data sheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

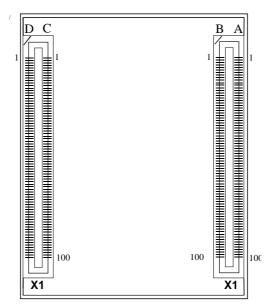

As *Figure 3* indicates, all controller signals extend to surface mount technology (SMT) connectors (0.635 mm) lining two sides of the module (referred to as phyCORE-connector; *refer to section 11*). This allows the phyCORE-MCF548x to be plugged into any target application like a "big chip".

*Figure 3: Pinout of the phyCORE-MCF548x (Bottom View)*

Many of the controller port pins accessible at the edges of the board have been assigned alternate functions that can be activated via software. phyCORE-MCF548x

*Table 1* provides an overview of the pinout of the phyCOREconnector, as well as descriptions of possible alternative functions. Reset state means the behavior of the signal while the processor's reset input /RSTI is active.

Please refer to the Freescale MCF548x User Manual/Data Sheet for details on the functions and features of controller signals and port pins.

| Pin Number     | Signal  | I/O | Comments                                     |

|----------------|---------|-----|----------------------------------------------|

| Pin Row X1A    | ~       |     |                                              |

| 1A             | EXTCLK  | Ι   | Clock input for GCLK3 of the XPLD            |

|                |         |     |                                              |

|                |         |     | 10 kOhm pull-down                            |

| 2A, 7A, 12A,   | GND     | -   | Ground 0 V                                   |

| 17A, 22A, 27A, |         |     |                                              |

| 32A, 37A, 42A, |         |     |                                              |

| 47A, 52A, 57A, |         |     |                                              |

| 62A, 67A, 72A, |         |     |                                              |

| 77A            |         |     |                                              |

| 3A             | /IRQ7   | Ι   | Interrupt input 7 of the ColdFire processor. |

|                |         | Ι   | GPI PIRQ7                                    |

|                |         |     | Reset state: GPI                             |

| 4A             | XPLD3_0 | I/O | XPLD GPIO                                    |

| 5A             | /FB_CS1 | 0   | Chip Select 1 of the ColdFire FlexBus.       |

|                |         |     | Reset state: high                            |

|                |         | I/O | PFBCS1 GPIO                                  |

| Pin Number | Signal     | I/O | Comments                               |

|------------|------------|-----|----------------------------------------|

| 6A         | XPLD3_1    |     | XPLD GPIO                              |

| 8A         | XPLD3_3    |     |                                        |

| 9A         | XPLD3_5    |     | Freely available I/O pins to implement |

| 10A        | XPLD3_6    |     | application-specific functionality.    |

| 11A        | XPLD3_8    |     |                                        |

| 13A        | XPLD3_11   |     |                                        |

| 14A        | XPLD3_13   |     |                                        |

| 15A        | XPLD3_14   |     |                                        |

| 16A        | XPLD3_16   |     |                                        |

| 18A        | XPLD3_19   |     |                                        |

| 19A        | XPLD3_21   |     |                                        |

| 20A        | XPLD3_22   |     |                                        |

| 21A        | XPLD3_24   |     |                                        |

| 23A        | XPLD3_27   |     |                                        |

| 24A        | XPLD3_29   |     |                                        |

| 25A        | XPLD3_30   |     |                                        |

| 26A        | XPLD3_32   |     |                                        |

| 28A        | XPLD3_35   |     |                                        |

| 29A        | XPLD0_1    |     |                                        |

| 30A        | XPLD0_2    |     |                                        |

| 31A        | XPLD0_4    |     |                                        |

| 33A        | XPLD0_7    |     |                                        |

| 34A        | XPLD0_9    |     |                                        |

| 35A        | XPLD0_10   |     |                                        |

| 36A        | XPLD0_12   |     |                                        |

| 38A        | XPLD0_15   |     |                                        |

| 39A        | XPLD0_17   |     |                                        |

| 40A        | XPLD0_18   |     |                                        |

| 41A        | /FB_CS4    | 0   | Chip Select 4 of the ColdFire FlexBus. |

|            |            |     | Reset state: high                      |

|            |            | I/O | PFBCS4 GPIO                            |

| 43A        | /DACK0     | 0   | DMA acknowledge 0                      |

|            |            | I/O | PDMA2 GPIO                             |

|            |            |     | Reset state: GPI                       |

|            |            | 0   | TOUT0 GP timer output 0                |

| 44A        | /DACK1     | 0   | DMA acknowledge 1                      |

|            |            | I/O | PDMA3 GPIO                             |

|            |            |     | Reset state: GPI                       |

| 15.        |            | 0   | TOUT1 GP timer output 1                |

| 45A        | /PCI_RESET | 0   | PCI reset                              |

| 161        |            |     | Reset state: Low                       |

| 46A        | /PCI_BR0   | I   | PCI bus request 0                      |

|            |            | I/O | PPCIBR0 GPIO                           |

|            |            | т   | Reset state: GPI                       |

|            |            | Ι   | TIN0 GP timer input 0                  |

|            | Signal               | T/O | Commonto                                           |

|------------|----------------------|-----|----------------------------------------------------|

| Pin Number | Signal               | I/O | Comments                                           |

| 48A        | /PCI_BR1             | I   | PCI bus request 1                                  |

|            |                      | I/O | PPCIBR1 GPIO                                       |

|            |                      | -   | Reset state: GPI                                   |

|            |                      | Ι   | TIN1 general purpose timer input 1                 |

| 49A        | /PCI_BR2             | Ι   | PCI bus request 2                                  |

|            |                      | I/O | PPCIBR0 GPIO                                       |

|            |                      |     | Reset state: GPI                                   |

|            |                      | Ι   | TIN2 general purpose timer input 2                 |

| 50A        | /PCI_BR3             | Ι   | PCI bus request 3                                  |

|            |                      | I/O | PPCIBR3 GPIO                                       |

|            |                      |     | Reset state: GPI                                   |

|            |                      | Ι   | TIN3 general purpose timer input 3                 |

| 51A        | /PCI_BR4             | Ι   | PCI bus request 4                                  |

|            |                      | I/O | PPCIBR4 GPIO                                       |

|            |                      | 10  | Reset state: GPI                                   |

|            |                      | Ι   | /IRQ4 interrupt input 4 of the ColdFire processor. |

| 53A        | PCI_AD31             | I/O | PCI address/data bus                               |

| 54A        | PCI_AD29             | 1/0 | Reset state: tristate                              |

| 55A        | PCI_AD27             |     | Bootstrap configuration <sup>1</sup> : FBMODE=1    |

| 56A        | PCI_AD27             |     | Bootstrap configuration <sup>2</sup> : FBMODE=1    |

| 59A        | PCI_AD23             |     |                                                    |

| 60A        | PCI_AD23             |     | Refer to A.1 for additional information.           |

| 61A        | PCI_AD19             |     |                                                    |

| 63A        | PCI_AD17             |     |                                                    |

| 71A        | PCI_AD14             |     |                                                    |

| 73A        | PCI_AD14             |     |                                                    |

| 74A        | PCI_AD12<br>PCI_AD10 |     |                                                    |

| 75A        | PCI_AD8              |     |                                                    |

| 76A        | PCI_AD7              |     |                                                    |

| 78A        | PCI_AD5              |     |                                                    |

| 79A        | PCI_AD3              |     |                                                    |

| 80A        | PCI_AD1              |     |                                                    |

|            |                      | 0   | FBADDRx FlexBus address lines                      |

| 58A        | /PCI_CXBE3           | I/O | PCI command/byte enable signal 3                   |

|            |                      |     | Reset state: tristate                              |

| 64A        | /PCI_CXBE2           | I/O | PCI command/byte enable signal 2                   |

| ντα        | /I CI_CADE2          | 1/0 |                                                    |

| 65 A       |                      | L/O | Reset state: tristate                              |

| 65A        | /PCI_IRDY            | I/O | PCI initiator ready signal                         |

|            |                      | T/O | Reset state: tristate                              |

| 66A        | /PCI_DEVSEL          | I/O | PCI device select signal                           |

|            |                      |     | Reset state: tristate                              |

| 68A        | /PCI_PERR            | I/O | PCI parity error signal                            |

|            |                      |     | Reset state: tristate                              |

| 69A        | /PCI_SERR            | I/O | PCI system error signal                            |

|            |                      |     | Reset state: tristate                              |

| 70°        | /PCI_CXBE1           | I/O | PCI command/byte enable signal 1                   |

|            |                      |     | Reset state: tristate                              |

<sup>1</sup> Refer to Table 3 for additional information to the system's start-up configuration.

| Pin Number     | Signal  | I/O | Comments                                     |

|----------------|---------|-----|----------------------------------------------|

| Pin Row X1B    |         |     |                                              |

| 1B             | CLK_EXT | 0   | Reference clock output of the processor's    |

|                |         |     | input clock.                                 |

| 2B             | /IRQ5   | Ι   | Interrupt input 5 of the ColdFire processor. |

|                |         | Ι   | GPI PIRQ5                                    |

|                |         |     | Reset state: GPI                             |

| 3B             | /IRQ6   | Ι   | Interrupt input 6 of the ColdFire processor. |

|                |         | Ι   | GPI PIRQ6                                    |

|                |         |     | Reset state: GPI                             |

| 4B, 9B, 14B,   | GND     |     | Ground 0 V                                   |

| 19B, 24B, 29B, |         |     |                                              |

| 34B, 39B, 44B, |         |     |                                              |

| 49B, 54B, 59B, |         |     |                                              |

| 64B, 69B, 74B, |         |     |                                              |

| 79B            |         |     |                                              |

| 5B             | /FB_CS2 | 0   | Chip Select 2 of the ColdFire FlexBus.       |

|                |         |     | Reset state: high                            |

|                |         | I/O | PFBCS2 GPIO                                  |

| 6B             | /FB_CS3 | 0   | Chip Select 3 of the ColdFire FlexBus.       |

|                |         |     | Reset state: high                            |

|                |         | I/O | PFBCS3 GPIO                                  |

| Pin Number | Signal   | I/O | Comments                                     |

|------------|----------|-----|----------------------------------------------|

| 7B         | XPLD3_2  | I/O | XPLD GPIO                                    |

| 8B         | XPLD3_4  |     |                                              |

| 10B        | XPLD3_7  |     | Free usable pins to implement application    |

| 11B        | XPLD3_9  |     | specific functionality.                      |

| 12B        | XPLD3_10 |     |                                              |

| 13B        | XPLD3_12 |     |                                              |

| 15B        | XPLD3_15 |     |                                              |

| 16B        | XPLD3_17 |     |                                              |

| 17B        | XPLD3_18 |     |                                              |

| 18B        | XPLD3_20 |     |                                              |

| 20B        | XPLD3_23 |     |                                              |

| 21B        | XPLD3_25 |     |                                              |

| 22B        | XPLD3_26 |     |                                              |

| 23B        | XPLD3_28 |     |                                              |

| 25B        | XPLD3_31 |     |                                              |

| 26B        | XPLD3_33 |     |                                              |

| 27B        | XPLD3_34 |     |                                              |

| 28B        | XPLD0_0  |     |                                              |

| 30B        | XPLD0_3  |     |                                              |

| 31B        | XPLD0_5  |     |                                              |

| 32B        | XPLD0_6  |     |                                              |

| 33B        | XPLD0_8  |     |                                              |

| 35B        | XPLD0_11 |     |                                              |

| 36B        | XPLD0_13 |     |                                              |

| 37B        | XPLD0_14 |     |                                              |

| 38B        | XPLD0_16 |     |                                              |

| 40B        | XPLD0_19 |     |                                              |

| 41B        | /FB_CS5  | 0   | Chip Select 5 of the ColdFire FlexBus.       |

|            |          |     | Reset state: high                            |

|            |          | I/O | PFBCS5 GPIO                                  |

| 42B        | /DREQ0   | Ι   | DMA request signal 0 of the processor.       |

|            |          | I/O | PDMA0 GPIO                                   |

|            |          |     | Reset state: GPI                             |

|            |          | Ι   | TIN1 GP timer input 1                        |

| 43B        | /DREQ1   | Ι   | DMA request signal 1 of the processor.       |

|            |          | I/O | PDMA1 GPIO                                   |

|            |          |     | Reset state: GPI                             |

|            |          | Ι   | TIN0 GP timer input 0                        |

|            |          | Ι   | /IRQ1 interrupt input 1                      |

| 45B        | CLK_PCI  | 0   | PCI reference clock output supplied from the |

|            |          |     | clock distribution device at U22.            |

| 46B        | GND      |     | Ground 0 V                                   |

| 47B        | /PCI_BG0 | 0   | PCI external bus grant signal 0.             |

|            |          | I/O | PPCIBG0 GPIO                                 |

|            |          | 1   | Reset state: GPI (PAR_PCIBG0)                |

|            |          | 0   | TOUT0 GP timer output 0                      |

| Pin Number | Signal     | I/O          | Comments                                         |

|------------|------------|--------------|--------------------------------------------------|

| 48B        | /PCI_BG1   | 0            | PCI external bus grant signal 1.                 |

| 40D        | /rCI_bOI   | I/O          | PPCIBG1 GPIO                                     |

|            |            | 1/U          | Reset state: GPI (PAR_PCIBG1)                    |

|            |            | 0            | TOUT1 GP timer output 1                          |

| 50B        | /PCI_BG2   | 0            | PCI external bus grant signal 2.                 |

| 300        | /PCI_BG2   | 1/O          | PPCIBG2 GPIO                                     |

|            |            | 1/0          |                                                  |

|            |            | 0            | Reset state: GPI (PAR_PCIBG2)                    |

| 51B        | /DCL DC2   |              | TOUT2 GP timer output 2                          |

| JID        | /PCI_BG3   | O<br>I/O     | PCI external bus grant signal 3.<br>PPCIBG3 GPIO |

|            |            | 1/0          |                                                  |

|            |            | 0            | Reset state: GPI (PAR_PCIBG3)                    |

| 52D        |            | 0            | TOUT3 GP timer output 3                          |

| 52B        | /PCI_BG4   | 0            | PCI external bus grant signal 0.                 |

|            |            | I/O          | PPCIBG4 GPIO                                     |

|            |            | 0            | Reset state: GPI (PAR_PCIBG3)                    |

| 525        |            | 0            | /TBST transfer burst signal of the FlexBus       |

| 53B        | PCI_AD30   | I/O          | PCI address/data bus                             |

| 55B        | PCI_AD28   |              | Reset state: tristate                            |

| 56B        | PCI_AD26   |              | Bootstrap configuration <sup>1</sup> : FBMODE=1  |

| 57B        | PCI_AD24   |              | <i>Refer to A.1 for additional information.</i>  |

| 60B        | PCI_AD22   |              | Refer to A.1 for additional information.         |

| 61B        | PCI_AD20   |              |                                                  |

| 62B        | PCI_AD18   |              |                                                  |

| 63B        | PCI_AD16   |              |                                                  |

| 70B        | PCI_AD15   |              |                                                  |

| 71B        | PCI_AD13   |              |                                                  |

| 72B        | PCI_AD11   |              |                                                  |

| 73B        | PCI_AD9    |              |                                                  |

| 76B        | PCI_AD6    |              |                                                  |

| 77B        | PCI_AD4    |              |                                                  |

| 78B        | PCI_AD2    |              |                                                  |

| 80B        | PCI_AD0    | 0            | EDADDE Elementation 1                            |

| 500        |            | 0            | FBADDRx FlexBus address lines                    |

| 58B        | PCI_IDSEL  | I            | PCI initialization device select signal          |

|            |            | <b>T</b> / O | Reset state: tristate                            |

| 65B        | /PCI_FRM   | I/O          | PCI frame signal                                 |

|            | D.GT       | <b>.</b>     | Reset state: tristate                            |

| 66B        | PCI_TRDY   | I/O          | PCI target Ready signal                          |

|            |            |              | Reset state: tristate                            |

| 67B        | /PCI_STOP  | I/O          | PCI stop signal                                  |

|            |            |              | Reset state: tristate                            |

| 68B        | PCI_PAR    | I/O          | PCI parity signal                                |

|            |            |              | Reset state: tristate                            |

| 75B        | /PCI_CXBE0 | I/O          | PCI command/byte enable signal 0                 |

|            |            |              | Reset state: tristate                            |

<sup>&</sup>lt;sup>1</sup> Refer to Table 3 for additional information to the system's start-up configuration.

© PHYTEC Messtechnik GmbH 2005 L-645e\_1

| Pin Number                | Signal        | I/O | Commonto                                        |

|---------------------------|---------------|-----|-------------------------------------------------|

| Pin Number<br>Pin Row X1C | Signal        | I/O | Comments                                        |

|                           | +21/2         | т   | Sumply welts as 12.2 VDC                        |

| 1C, 2C                    | +3V3          | Ι   | Supply voltage +3.3 VDC                         |

| 3C, 7C, 12C,              | GND           | -   | Ground 0 V                                      |

| 17C, 22C, 27C,            |               |     |                                                 |

| 32C, 37C, 42C,            |               |     |                                                 |

| 47C, 52C, 57C,            |               |     |                                                 |

| 62C, 67C                  | X / X X 7 X / | T   |                                                 |

| 4C, 5C                    | VIN5V         | Ι   | Alternatively supply voltage +5 VDC for         |

|                           |               |     | CAN transceivers. Refer the description of      |

|                           |               | -   | jumper J36 in <i>Table 2</i> .                  |

| 6C                        | VBAT          | Ι   | Connection for external battery (+) 2.4-3.3 V   |

|                           |               |     | to supply (backup) the RTC and the serial       |

|                           |               |     | memory.                                         |

| 8C                        | XPLD1_2       | I/O | XPLD GPIO                                       |

| 9C                        | XPLD1_3       |     |                                                 |

| 26C                       | XPLD1_4       |     | Freely available pins to implement              |

| 48C                       | XPLD1_5       |     | application-specific functionality.             |

| 49C                       | XPLD1_7       |     |                                                 |

| 50C                       | XPLD1_8       |     |                                                 |

| 51C                       | XPLD1_10      |     |                                                 |

| 53C                       | XPLD0_34      |     |                                                 |

| 54C                       | XPLD0_32      |     |                                                 |

| 55C                       | XPLD0_31      |     |                                                 |

| 56C                       | XPLD0_29      |     |                                                 |

| 58C                       | XPLD0_26      |     |                                                 |

| 59C                       | XPLD0_24      |     |                                                 |

| 60C                       | XPLD0_22      |     |                                                 |

| 61C                       | XPLD0_20      |     |                                                 |

| 10C                       | /RSTI         | I/O | Reset input signal of the ColdFire processor.   |

|                           |               |     | Reset signal supplied by the voltage            |

|                           |               |     | supervision device U23 to the processor's       |

|                           |               |     | /RSTI reset input pin. Can be driven            |

|                           |               |     | externally. Input resistance is 1kOhm. Do not   |

|                           |               |     | connect push buttons e.g. to this pin. This pin |

|                           |               |     | should be controlled by logic devices only. It  |

|                           |               |     | is recommended to control the system reset      |

|                           |               |     | via the /RESIN signal located at X2D10.         |

|                           |               |     | Asserting the /RESIN signal results in          |

|                           |               |     | asserting /RSTI from the voltage supervisor.    |

|                           |               |     | The voltage supervisor adds a reset delay of    |

|                           |               |     | 200 ms for /RSTI. That means /RSTI will         |

|                           |               |     | stay active 200 ms after /RESIN is released.    |

| 11C                       | /RSTO         | 0   | Reset output signal of the ColdFire             |

|                           |               |     | processor.                                      |

|                           |               |     | Reset state: low                                |

|                           |               |     | Refer to A.1 for additional information.        |

| Pin Number | Signal    | I/O      | Comments                                       |

|------------|-----------|----------|------------------------------------------------|

| 13C        | TXD3_TTL  | 0        | PSC3 transmit data signal                      |

|            |           | I/O      | PPSC3PSC24 GPIO                                |

|            |           |          | Reset state: GPI                               |

| 14C        | RXD3_TTL  | Ι        | PSC3 receive data signal                       |

| _          |           | I/O      | PPSC3PSC25 GPIO                                |

|            |           |          | Reset state: GPI                               |

| 15C        | /CTS3_TTL | 0        | PCS3 clear to send signal                      |

|            |           | I/O      | PPSC3PSC27 GPIO                                |

|            |           |          | Reset state: GPI                               |

|            |           | Ι        | PSC3BCLK PSC3 modem clock                      |

| 16C        | /RTS3_TTL | Ι        | PSC3 request to send signal                    |

|            |           | I/O      | PPSC3PSC26 GPIO                                |

|            |           |          | Reset state: GPI                               |

|            |           | Ι        | PSC3FSYNC PSC3 frame sync                      |

| 18C        | CAN_H1    | I/O      | CAN_High output from the CAN transceiver       |

|            |           |          | of the second CAN interface.                   |

| 19C        | RXD1_TTL  | Ι        | PSC1 receive data signal                       |

|            |           | I/O      | PPSC1PSC05 GPIO                                |

|            |           |          | Reset state: GPI                               |

| 20C        | TXD1_TTL  | 0        | PSC1 transmit data signal                      |

|            |           | I/O      | PPSC1PSC04 GPIO                                |

|            |           |          | Reset state: GPI                               |

| 21C        | RXD1      | Ι        | RxD input on the RS-232 transceiver for the    |

| 220        |           |          | second ColdFire UART PSC1.                     |

| 23C        | TXD1      | 0        | TxD output on the RS-232 transceiver for the   |

| 240        |           | т        | second ColdFire UART PSC1.                     |

| 24C        | /RTS1_TTL | I<br>I/O | PSC1 request to send signal<br>PPSC1PSC06 GPIO |

|            |           | 1/0      | Reset state: GPI                               |

|            |           | Ι        | PSC1FSYNC PSC1 frame sync                      |

| 25C        | /CTS1_TTL | 0        | PCS1 clear to send signal                      |

| 250        | /CISI_IIL | I/O      | PPSC1PSC07 GPIO                                |

|            |           | 1.0      | Reset state: GPI                               |

|            |           | Ι        | PSC1BCLK PSC1 modem clock                      |

| 28C        | DSPI_CS5  | 0        | QSPI Chip Select signal 5                      |

|            |           | I/O      | PDSPI6 GPIO                                    |

|            |           |          | Reset state: GPI                               |

| 30C        | DSPI_CS2  | 0        | QSPI Chip Select signal 5                      |

|            | —         | I/O      | PDSPI4 GPIO                                    |

|            |           |          | Reset ctate: GPI                               |

|            |           | 0        | TOUT2 GP timer output 2                        |

|            |           | 0        | CANTX1 FlexCAN transmit 1                      |

| 31C        | SCL       | I/O      | I <sup>2</sup> C serial clock signal           |

|            |           | I/O      | PFECI2C0 GPIO                                  |

|            |           |          | Reset state: GPI                               |

| Pin Number | Signal    | I/O                                           | Comments                                                                                                            |  |

|------------|-----------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| 33C        | E0 LED0   | 0                                             | Ethernet 0 LED output for link/activity                                                                             |  |

|            |           |                                               | monitoring.                                                                                                         |  |

| 34C        | E0_LED1   | O Ethernet 0 LED output for speed monitoring. |                                                                                                                     |  |

| 35C        | E0_RX-    | Ι                                             | Ethernet 0 negative receive input.                                                                                  |  |

| 36C        | E0_TX-    | 0                                             | Ethernet 0 negative transmit output.                                                                                |  |

| 38C        | USBVBUS   | Ι                                             | USB voltage monitor input                                                                                           |  |

| 39C        | E1_LED0   | 0                                             | Ethernet 1 LED output for link/activity                                                                             |  |

|            |           |                                               | monitoring.                                                                                                         |  |

| 40C        | E1_RX-    | Ι                                             | Ethernet 1 negative receive input.                                                                                  |  |

| 41C        | E1_TX-    | 0                                             | Ethernet 1 negative transmit output.                                                                                |  |

| 43C        | TIN0      | Ι                                             | GP timer input 0                                                                                                    |  |

|            |           |                                               | Reset state: GPI                                                                                                    |  |

| 44C        | TIN1      | Ι                                             | GP timer input 1                                                                                                    |  |

|            |           |                                               | Reset State: GPI                                                                                                    |  |

| 45C        | TOUT1     | 0                                             | GP timer output 1                                                                                                   |  |

|            |           |                                               | Reset state: tristate                                                                                               |  |

| 46C        | TOUT2     | 0                                             | GP timer output 2                                                                                                   |  |

|            |           |                                               | Reset state: tristate                                                                                               |  |

| 63C        | DSCLK     | Ι                                             | BDM debug serial clock input                                                                                        |  |

|            |           |                                               | Bootstrap configuration: MTMOD0=0                                                                                   |  |

|            |           | Ι                                             | /TRST JTAG reset                                                                                                    |  |

| 64C        | TCK       | Ι                                             | JTAG test clock input                                                                                               |  |

| 65C        | DSO       | 0                                             | BDM debug serial output                                                                                             |  |

|            |           |                                               | Reset state: high                                                                                                   |  |

|            |           |                                               | Bootstrap configuration: MTMOD0=0                                                                                   |  |

|            |           |                                               | TDO JTAG data output                                                                                                |  |

| 66C        | PSTDDATA6 | 0                                             | ColdFire processor status debug data output                                                                         |  |

| 68C        | PSTDDATA4 |                                               |                                                                                                                     |  |

| 69C        | PSTDDATA2 |                                               |                                                                                                                     |  |

| 70C        | /TA       | Ι                                             | Transfer acknowledge on the FlexBus                                                                                 |  |

|            |           |                                               | Reset state: tristate                                                                                               |  |

|            |           | I/O                                           | PFBCTL1 GPIO (PAR_TA=0)                                                                                             |  |

| 71C        | PSTCLK    | 0                                             | Processor clock output                                                                                              |  |

|            |           |                                               | Supplies 100MHz with 50MHz input clock.                                                                             |  |

| 700        |           | T                                             | Reset state: high                                                                                                   |  |

| 73C        | XPLD_TCK  | I                                             | XPLD JTAG clock input                                                                                               |  |

| 74C        | XPLD_TMS  | Ι                                             | XPLD JTAG test mode select input.                                                                                   |  |

| 750        | D 4 CO    | 0                                             | 10kOhm pull-up                                                                                                      |  |

| 75C        | DAC0      | 0                                             | Analog output of the digital to analog converter $U_{14}$ . This desires is convected to the $J_{2C}^{2C}$ has with |  |

|            |           |                                               | U14. This device is connected to the $I^2C$ bus with                                                                |  |

| 760        |           | т                                             | slave address 0x98/0x99.                                                                                            |  |

| 76C        | ADC6      | Ι                                             | Analog input of the analog to digital                                                                               |  |

| 78C        | ADC3      |                                               | converter U13. This device is connected to $V^2$                                                                    |  |

| 79C        | ADC1      |                                               | the $I^2C$ bus with slave address $0x90/0x91$ .                                                                     |  |

| 80C        | ADC0      |                                               | For detailed description refer to the                                                                               |  |

|            |           |                                               | ADC7828 Data Sheet provided by Texas                                                                                |  |

|            |           |                                               | Instruments/Burr-Brown.                                                                                             |  |

| Pin Number     | Signal     | I/O | Comments                                                                        |  |

|----------------|------------|-----|---------------------------------------------------------------------------------|--|

| Pin Row X1D    | ~-8        |     |                                                                                 |  |

| 1D, 2D, 4D, 5D | +3V3       | Ι   | Supply voltage +3.3 VDC                                                         |  |

| 3D, 9D, 14D,   | GND        | -   | Ground 0 V                                                                      |  |

| 19D, 24D, 29D, |            |     |                                                                                 |  |

| 34D, 39D, 44D, |            |     |                                                                                 |  |

| 49D, 54D, 59D, |            |     |                                                                                 |  |

| 64D, 69D       |            |     |                                                                                 |  |

| 6D             | VPD        | 0   | Power-down supply voltage VPD is                                                |  |

|                |            |     | generated by VBAT or $+3V3$ using a diode                                       |  |

|                |            |     | switching circuitry. VPD serves as supply                                       |  |

|                |            |     | voltage for the Real-Time Clock and the                                         |  |

|                |            |     | serial EPROM.                                                                   |  |

| 7D             | XPLD1_0    | I/O | XPLD GPIO                                                                       |  |

| 8D             | XPLD1_1    |     |                                                                                 |  |

| 50D            | XPLD1_6    |     | Freely available pins to implement                                              |  |

| 51D            | XPLD1_9    |     | application specific functionality.                                             |  |

| 52D            | XPLD0_35   |     |                                                                                 |  |

| 53D            | XPLD0_33   |     |                                                                                 |  |

| 55D            | XPLD0_30   |     |                                                                                 |  |

| 56D            | XPLD0_28   |     |                                                                                 |  |

| 57D            | XPLD0_27   |     |                                                                                 |  |

| 58D            | XPLD0_25   |     |                                                                                 |  |

| 60D            | XPLD0_23   |     |                                                                                 |  |

| 61D            | XPLD0_21   | T   |                                                                                 |  |

| 10D            | /RESIN     | Ι   | Manual reset input of the voltage supervisor device U23.                        |  |

|                |            |     |                                                                                 |  |

|                |            |     | Asserting /RESIN results in asserting the system reset /RSTI. After negation of |  |

|                |            |     | /RESIN the system reset /RSTI stays active                                      |  |

|                |            |     | for additional 200ms (reset delay). This                                        |  |

|                |            |     | signal can be used for connection of a reset                                    |  |

|                |            |     | push button e.g.                                                                |  |

|                |            |     | Signal connected to +3V3 via 10kOhm pull-                                       |  |

|                |            |     | up resistor.                                                                    |  |

| 11D            | TXD2_TTL   | 0   | PSC2 transmit data signal                                                       |  |

|                | - <u> </u> | I/O | PPSC3PSC20 GPIO                                                                 |  |

|                |            |     | Reset state: GPI                                                                |  |

| 12D            | RXD2_TTL   | Ι   | PSC2 receive data signal                                                        |  |

|                | _          | I/O | PPSC3PSC021 GPIO                                                                |  |

|                |            |     | Reset state: GPI                                                                |  |

| 13D            | /CTS2_TTL  | 0   | PCS2 clear to send signal                                                       |  |

|                |            | I/O | PPSC3PSC23 GPIO                                                                 |  |

|                |            |     | Reset state: GPI                                                                |  |

|                |            | Ι   | PSC2BCLK PSC2 modem clock                                                       |  |

|                |            | Ι   | CANRX0 FlexCAN receive input 0                                                  |  |

| Pin Number | Signal    | I/O      | Comments                                                           |

|------------|-----------|----------|--------------------------------------------------------------------|

| 15D        | /RTS2_TTL | I        | PSC2 request to send signal                                        |

| 15D        | /KI52_IIL | I/O      | PPSC3PSC22 GPIO                                                    |

|            |           | 1/0      | Reset state: GPI                                                   |

|            |           | Ι        | PSC2FSYNC PSC2 frame sync                                          |

|            |           | 0        | CANTX0 FlexCAN transmit output 0                                   |

| 16D        | RXD0_TTL  | I        | PSC0 receive data signal                                           |

| 10D        | KAD0_IIL  | I/O      | PPSC1PSC01 GPIO                                                    |

|            |           | 1/0      | Reset state: GPI                                                   |

| 17D        | TXD0_TTL  | 0        | PSC0 transmit data signal                                          |

| 170        | IAD0_IIL  | I/O      | PPSC1PSC00 GPIO                                                    |

|            |           | 1/0      | Reset state: GPI                                                   |

| 18D        | CAN_L1    | I/O      | CANL output on the CAN transceiver for the                         |

| 16D        | CAN_LI    | 1/0      | second CAN interface.                                              |

| 20D        | CAN LO    | L/O      |                                                                    |

| 20D        | CAN_L0    | I/O      | CANL output on the CAN transceiver for the first CAN interface.    |

| 21D        | CAN HO    | I/O      |                                                                    |

| 21D        | CAN_H0    | 1/0      | CANH output on the CAN transceiver for the first CAN interface.    |

| 22D        | DVD0      | T        | RxD input on the RS-232 transceiver for the first                  |

| 220        | RXD0      | Ι        | <b></b>                                                            |