# phyCARD-M

# Hardware Manual

Document No.: L-750e\_1

SBC Prod. No.: PCA-A-M1-xxx

CB Prod. No.: PBA-A-01

Edition: June 2010

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark (TM) and copyright (©) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC Messtechnik GmbH assumes no responsibility for any inaccuracies. PHYTEC Messtechnik GmbH neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC Messtechnik GmbH reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages which might result.

Additionally, PHYTEC Messtechnik GmbH offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC Messtechnik GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

#### © Copyright 2010 PHYTEC Messtechnik GmbH, D-55129 Mainz.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC Messtechnik GmbH.

|                       | EUROPE                                                                           | NORTH AMERICA                          |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------|

| Address:              | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | 203 Parfitt Way SW, Suite G100         |

| Ordering Information: | +49 (800) 0749832<br>order@phytec.de                                             | 1 (800) 278-9913<br>sales@phytec.com   |

| Technical<br>Support: | +49 (6131) 9221-31<br>support@phytec.de                                          | 1 (800) 278-9913<br>support@phytec.com |

| Fax:                  | +49 (6131) 9221-33                                                               | 1 (206) 780-9135                       |

| Web Site:             | http://www.phytec.de                                                             | http://www.phytec.com                  |

1<sup>st</sup> Edition June 2010

|           |      | Figures                                                 |          |

|-----------|------|---------------------------------------------------------|----------|

|           |      | Tables                                                  |          |

|           |      | ons, Abbreviations and Acronyms                         |          |

|           |      |                                                         |          |

| 1         |      | oduction                                                |          |

|           | 1.1  | - · · · · · · · · · · · · · · · · · · ·                 |          |

|           | 1.2  | 1 2                                                     |          |

| 2         | 1.3  | Minimum Requirements to Operate the phyCARD-M           |          |

| 3         |      | Description  ipers                                      |          |

| <b>4</b>  |      | ver                                                     |          |

| 4         | 4.1  | Primary System Power (VCC_3V3)                          |          |

|           | 4.1  | Standby Voltage (VBAT)                                  |          |

|           | 4.3  | On-board Voltage Regulator (U1)                         | 20<br>28 |

|           | 4.4  | Supply Voltage for external Logic                       | 20<br>30 |

| 5         |      | ver Management                                          |          |

| 6         |      | tem Configuration and Booting                           |          |

| 7         | -    | tem Memory                                              |          |

| •         | ·    | DDR2-SDRAM (U8 - U11)                                   |          |

|           |      | NAND Flash Memory (U13)                                 |          |

|           | 7.3  | I <sup>2</sup> C EEPROM (U6)                            |          |

|           |      | 7.3.1 Setting the EEPROM Lower Address Bits (J1, J3, J4 |          |

|           |      | 7.3.2 EEPROM Write Protection Control (J16)             |          |

|           | 7.4  | Memory Model                                            |          |

| 8         | SD   | / MMC Card Interfaces                                   | 42       |

| 9         | Seri | ial Interfaces                                          | 44       |

|           | 9.1  | Universal Asynchronous Interface                        | 45       |

|           | 9.2  | USB-OTG Interface                                       |          |

|           | 9.3  | USB-Host Interface                                      | 47       |

|           | 9.4  | Ethernet Interface                                      | 48       |

|           |      | 9.4.1 PHY Physical Layer Transceiver (U7)               |          |

|           |      | 9.4.2 MAC Address                                       |          |

|           | 9.5  |                                                         |          |

|           | 9.6  | SPI Interface                                           |          |

|           | 9.7  | Synchronous Serial Interface (SSI)                      |          |

| 10        |      | neral Purpose I/Os                                      |          |

| 11        |      | oug Interface (X1)                                      |          |

| <b>12</b> |      | DS Display Interface                                    |          |

|           |      | Signal configuration (J22)                              |          |

| 10        |      | 2 LVDS Display Interface pixel mapping                  |          |

| 13        | LVI  | DS Camera Interface                                     | 60       |

|           | 13.1 Signal configuration (J21)                      | 60  |

|-----------|------------------------------------------------------|-----|

| <b>14</b> | Technical Specifications                             |     |

| <b>15</b> | Component Placement Diagram                          | 64  |

| <b>16</b> | Hints for Handling the phyCARD-M                     | 66  |

| <b>17</b> | The phyCARD-M on the phyBase                         | 67  |

|           | 17.1 Concept of the phyBASE Board                    | 68  |

|           | 17.2 Overview of the phyBASE Peripherals             | 70  |

|           | 17.2.1 Connectors and Pin Header                     | 71  |

|           | 17.2.2 Switches                                      | 72  |

|           | 17.2.3 LEDs                                          | 76  |

|           | 17.2.4 Jumpers                                       | 78  |

|           | 17.3 Functional Components on the phyBASE Board      |     |

|           | 17.3.1 phyCARD-M SBC Connectivity (X27)              |     |

|           | 17.3.2 Power Supply (X28)                            | 83  |

|           | 17.3.3 RS-232 Connectivity (P1)                      |     |

|           | 17.3.4 Ethernet Connectivity (X10)                   | 88  |

|           | 17.3.5 USB Host Connectivity (X7, X8, X9, X30, X33)  |     |

|           | 17.3.6 USB OTG Connectivity (X29)                    |     |

|           | 17.3.7 Display / Touch Connectivity (X6, X32)        |     |

|           | 17.3.7.1 Display Data Connector (X6)                 |     |

|           | 17.3.7.2 Display Power Connector (X32)               |     |

|           | 17.3.7.3 Touch Screen Connectivity                   |     |

|           | 17.3.8 Camera Interface (X5)                         |     |

|           | 17.3.9 Audio Interface (X1,X2,X3)                    |     |

|           | 17.3.10 I <sup>2</sup> C Connectivity                |     |

|           | 17.3.11 SPI Connectivity                             |     |

|           | 17.3.12 User programmable GPIOs                      |     |

|           | 17.3.13 Expansion connectors (X8A, X9A)              |     |

|           | 17.3.14 Security Digital Card/ MultiMedia Card (X26) |     |

|           | 17.3.15 Boot Mode Selection (JP1)                    |     |

|           | 17.3.16 System Reset Button (S1)                     |     |

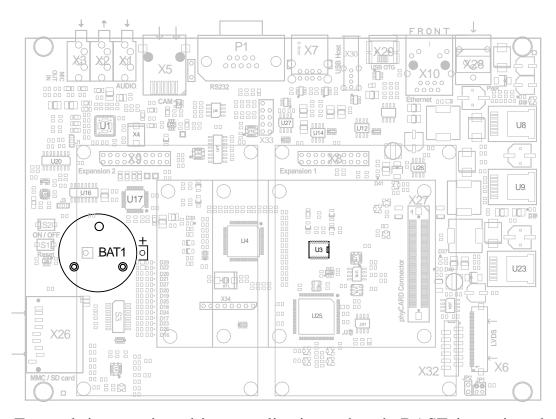

|           | 17.3.17 RTC at U3                                    |     |

|           | 17.3.18 PLD at U25                                   |     |

|           | 17.3.19 Carrier Board Physical Dimensions            |     |

| 18        | Revision History                                     |     |

| Ind       | ex                                                   | 116 |

# **Index of Figures**

| Figure 1:  | Block Diagram of the phyCARD-M                                   | 10 |

|------------|------------------------------------------------------------------|----|

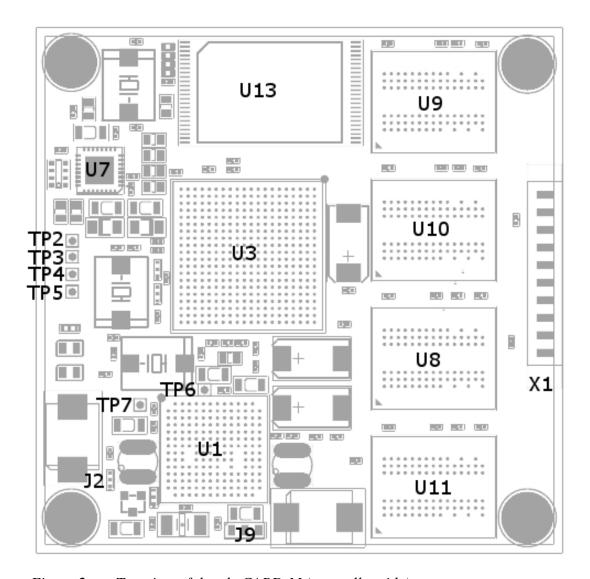

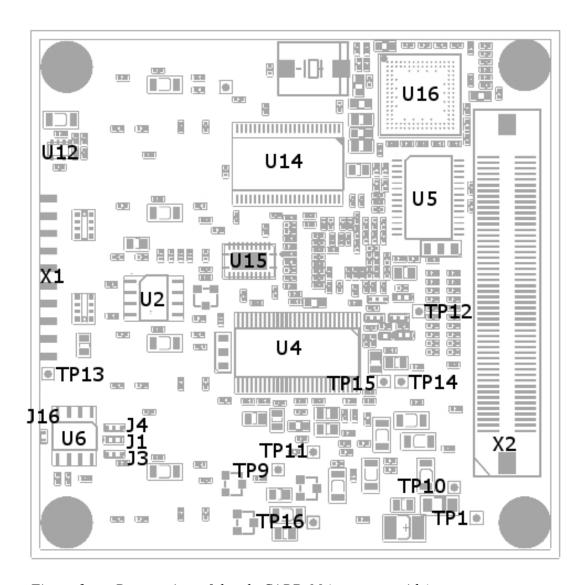

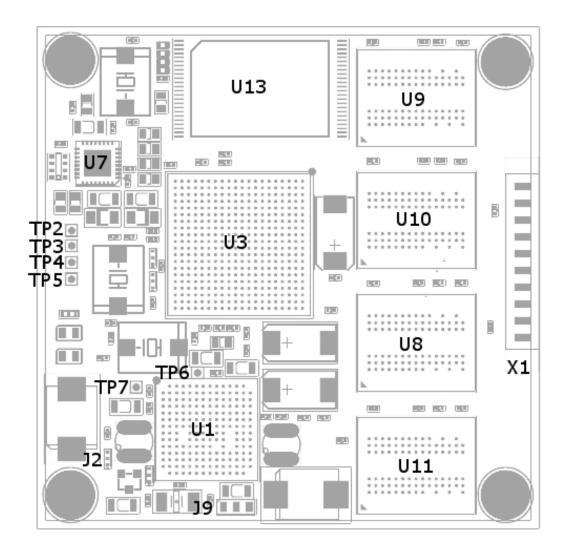

| Figure 2:  | Top view of the phyCARD-M (controller side)                      | 11 |

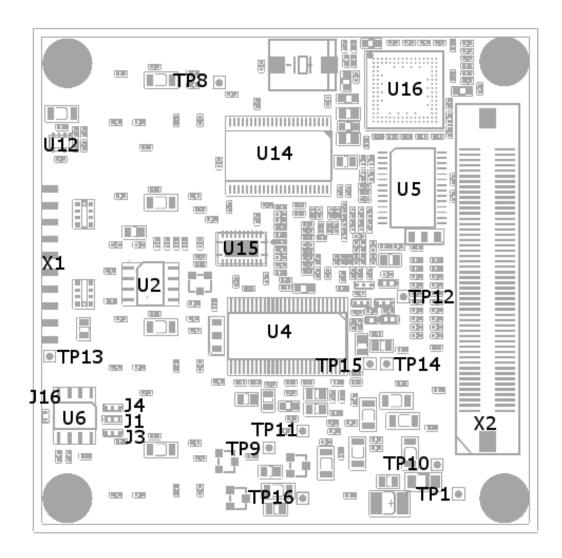

| Figure 3:  | Bottom view of the phyCARD-M (connector side)                    | 12 |

| Figure 4:  | Pin-out of the phyCARD-Connector (top view, with section insert) |    |

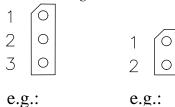

| Figure 5:  | Typical jumper pad numbering scheme                              | 22 |

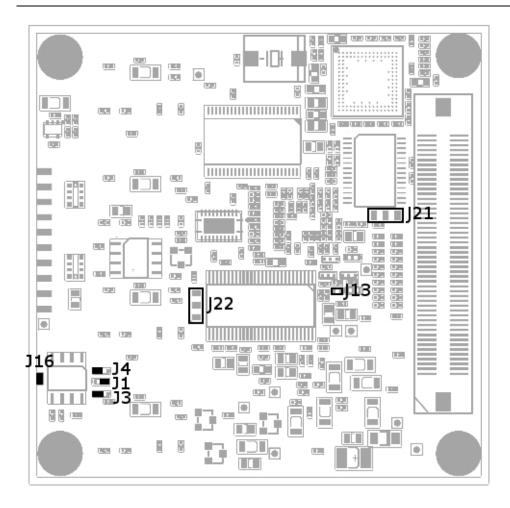

| Figure 6:  | Jumper locations (top view)                                      | 23 |

| Figure 7:  | Jumper locations (bottom view)                                   | 24 |

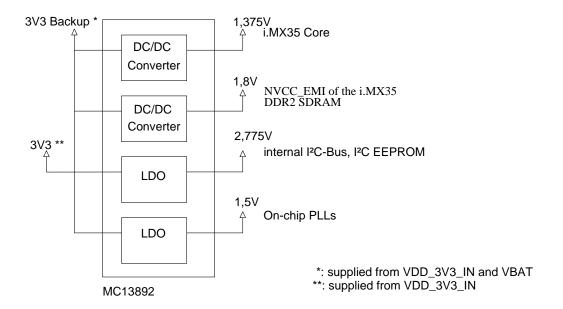

| Figure 8:  | Power Supply Diagram                                             | 29 |

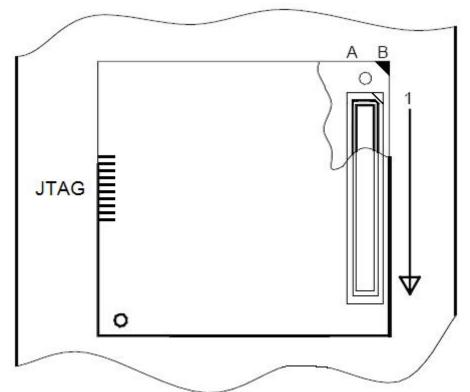

| Figure 9:  | JTAG interface at X1 (top view)                                  | 54 |

| Figure 10: | JTAG interface at X1 (bottom view)                               | 55 |

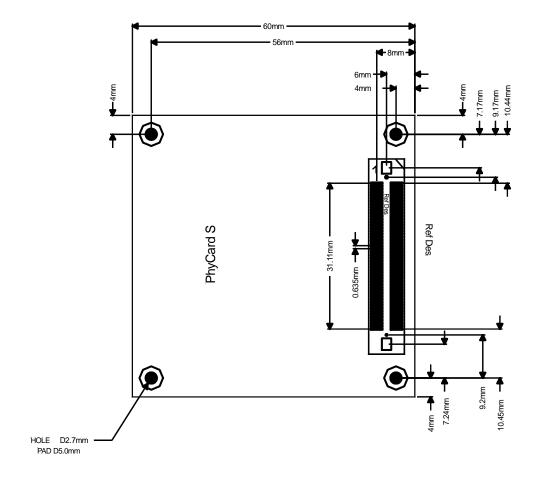

| Figure 11: | Physical dimensions                                              | 61 |

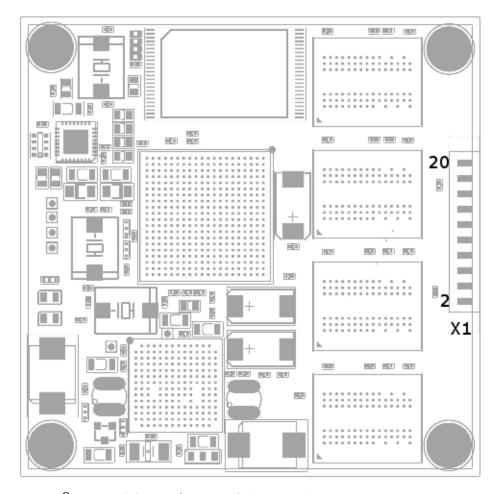

| Figure 12: | phyCARD-M component placement (top view)                         | 64 |

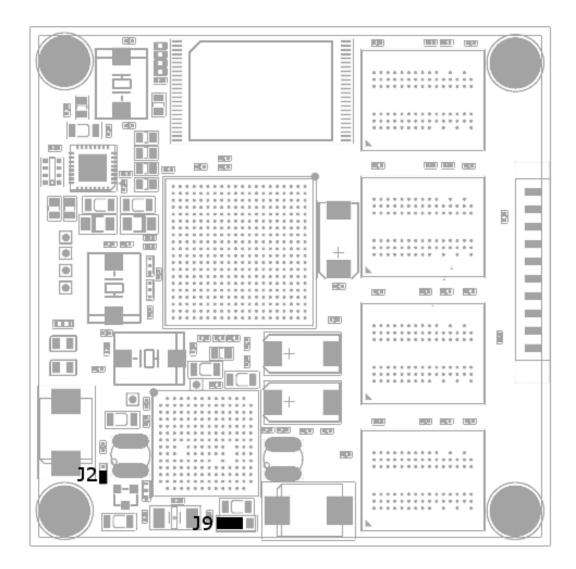

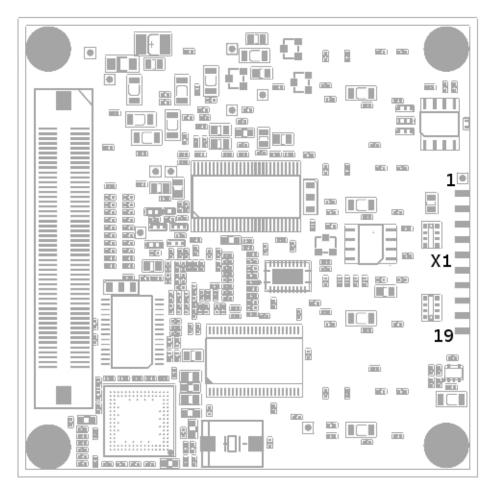

| Figure 13: | phyCARD-M component placement (bottom view)                      | 65 |

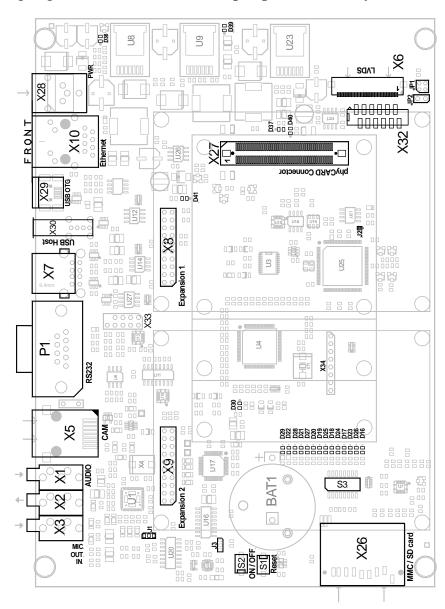

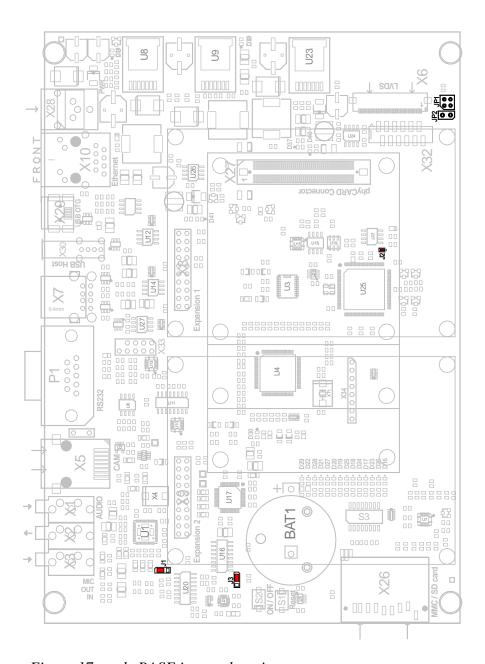

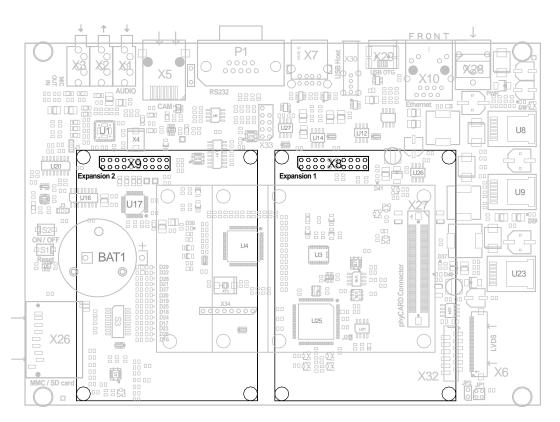

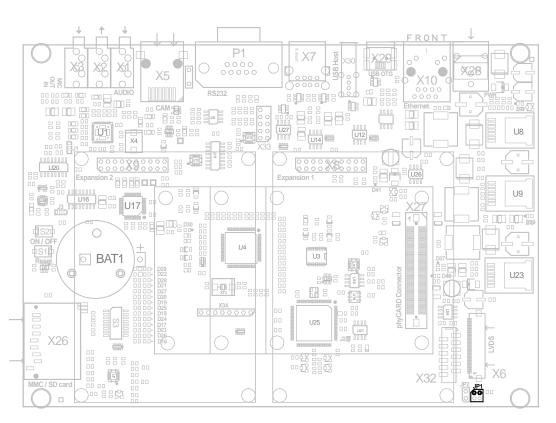

| Figure 14: | phyBASE (phyCARD-M Carrier Board)                                | 69 |

| Figure 15: | phyBASE Overview of Connectors, LEDs and Buttons                 | 70 |

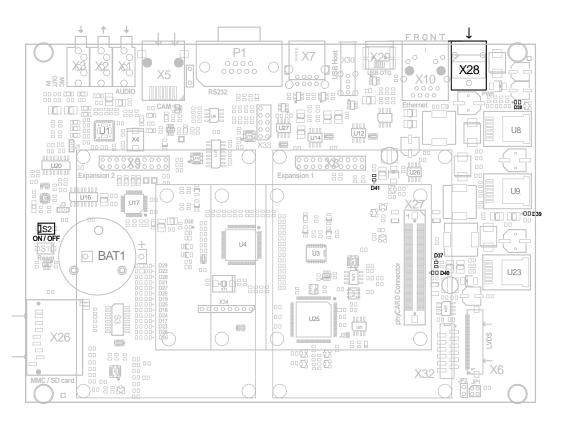

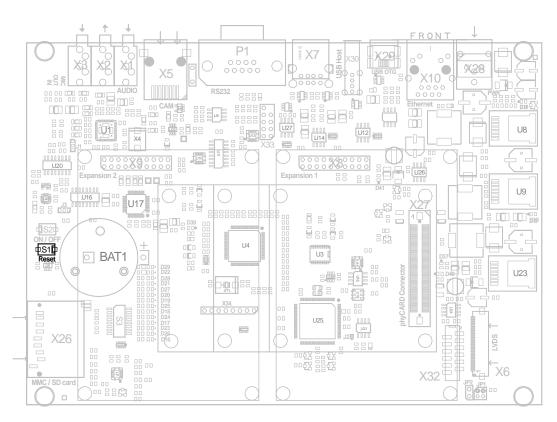

| Figure 16: | Typical jumper numbering scheme                                  | 78 |

| Figure 17: | phyBASE jumper locations                                         | 79 |

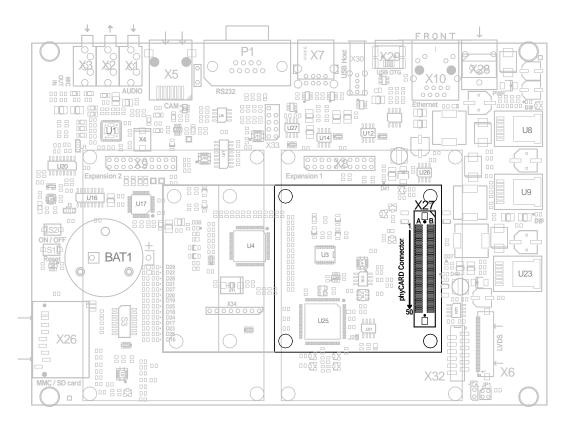

| Figure 18: | phyCARD-M SBC Connectivity to the Carrier Board                  | 82 |

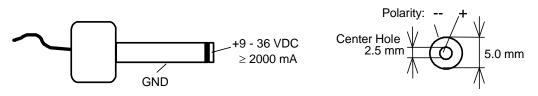

| Figure 19: | Power adapter                                                    | 83 |

| Figure 20: | Connecting the Supply Voltage at X28                             | 84 |

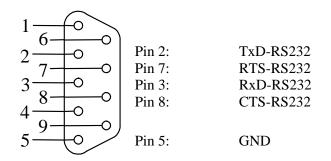

| Figure 21: | UART1 connection interface at connector P1                       | 86 |

| Figure 22: | UART1 connector P1 signal description                            | 87 |

| Figure 23: | Ethernet interface at connector X10                              | 88 |

| Figure 24: | USB host interface at connector X7, X30, X33                     | 89 |

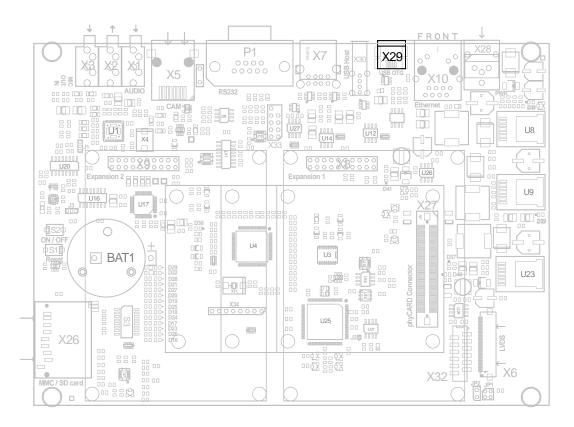

| Figure 25: | USB OTG interface at connector X29                               | 91 |

| Figure 26: | Universal LVDS interface at connector X6                         | 92 |

## phyCARD-M [PCA-A-M1-xxx]

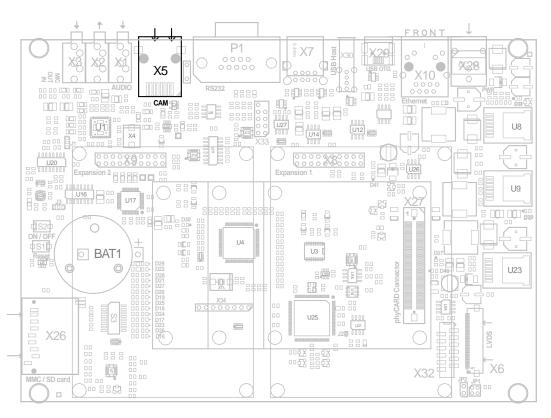

| Figure 27: | Camera interface at connectors X5      | 99  |

|------------|----------------------------------------|-----|

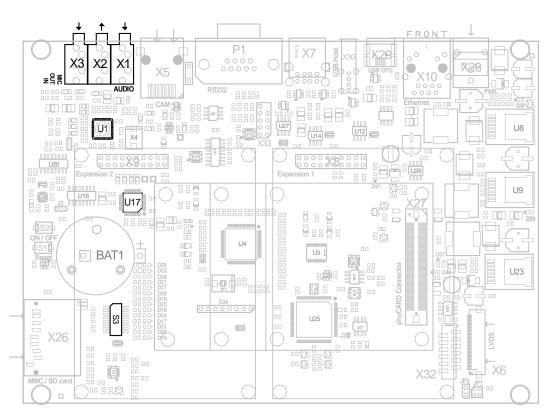

| Figure 28: | Audio interface at connectors X1,X2,X3 | 101 |

| Figure 29: | Expansion connector X8A, X9A           | 105 |

| Figure 30: | SD Card interface at connector X26     | 108 |

| Figure 31: | Boot Mode Selection Jumper JP1         | 109 |

| Figure 32: | System Reset Button S1                 | 111 |

| Figure 33: | Carrier Board Physical Dimensions      | 114 |

## **Index of Tables**

| Table 1:  | Abbreviations and Acronyms used in this Manual | 2  |

|-----------|------------------------------------------------|----|

| Table 2:  | X-Arc Bus Pin-out                              | 17 |

| Table 3:  | Pin-out of the phyCARD-Connector X2            | 21 |

| Table 4:  | Jumper settings                                | 26 |

| Table 5:  | Power Management Pins                          | 31 |

| Table 6:  | Power States                                   | 32 |

| Table 7:  | Power management jumpers J2 and J9             | 33 |

| Table 8:  | Boot Modes of i.MX35 module                    | 35 |

| Table 9:  | Further Boot Configuration Pins                | 36 |

| Table 10: | Compatible NAND Flash devices                  | 39 |

| Table 11: | U6 EEPROM I2C address via J1, J3, and J4       | 40 |

| Table 12: | EEPROM write protection states via J16         | 41 |

| Table 13: | Location of SD/ MMC Card interface signals     | 42 |

| Table 14: | Location of the UART signals                   | 45 |

| Table 15: | Location of the USB-OTG signals                | 46 |

| Table 16: | Location of the USB-Host signals               | 47 |

| Table 17: | Location of the Ethernet signals               | 48 |

| Table 18: | Fast Ethernet controller memory map            | 49 |

| Table 19: | I <sup>2</sup> C Interface Signal Location     | 50 |

| Table 20: | SPI Interface Signal Location                  | 51 |

| Table 21: | SSI Interface Signal Location                  | 52 |

| Table 22: | Location of GPIO and IRQ pins                  | 53 |

| Table 23: | JTAG connector X1 signal assignment            | 56 |

| Table 24: | Display Interface Signal Location              | 57 |

| Table 25: | Pixel mapping of 18-bit LVDS display interface | 58 |

| Table 26: | Pixel mapping of 24-bit LVDS display interface | 59 |

|           |                                                |    |

## phyCARD-M [PCA-A-M1-xxx]

| Table 27: | Camera Interface Signal Location                | 60  |

|-----------|-------------------------------------------------|-----|

| Table 28: | phyBASE Connectors and Pin Headers              | 71  |

| Table 29: | phyBASE push buttons descriptions               | 72  |

| Table 30: | phyBASE DIP-Switch S3 descriptions              | 75  |

| Table 31: | phyBASE LEDs descriptions                       | 76  |

| Table 32: | phyBASE jumper descriptions                     | 81  |

| Table 33: | LEDs assembled on the Carrier Board             | 84  |

| Table 34: | Distribution of the USB hub's (U4) ports        | 90  |

| Table 35: | Universal USB pin header X33 signal description | 90  |

| Table 36: | Display data connector signal description       | 94  |

| Table 37: | SPI and GPIO connector selection                | 95  |

| Table 38: | LVDS power connector X32 signal description     | 96  |

| Table 39: | Selection of the touch screen controller        | 97  |

| Table 40: | PHYTEC camera connector X5                      | 100 |

| Table 41: | Selection of the audio codec                    | 102 |

| Table 42: | I <sup>2</sup> C connectivity                   | 102 |

| Table 43: | I <sup>2</sup> C addresses in use               | 103 |

| Table 44: | SPI connector selection                         | 104 |

| Table 45: | SPI and GPIO connector selection                | 106 |

| Table 46: | PHYTEC expansion connector X8A, X9A             | 107 |

## **Conventions, Abbreviations and Acronyms**

This hardware manual describes the PCA-A-M1 Single Board Computer in the following referred to as phyCARD-M. The manual specifies the phyCARD-M's design and function. Precise specifications for the Freescale i.MX35 microcontrollers can be found in the enclosed microcontroller Data Sheet/User's Manual.

#### **Conventions**

The conventions used in this manual are as follows:

- Signals that are preceded by a "n", "/", or "#"character (e.g.: nRD, /RD, or #RD), or that have a dash on top of the signal name (e.g.: RD) are designated as active low signals. That is, their active state is when they are driven low, or are driving low.

- A "0" indicates a logic zero or low-level signal, while a "1" represents a logic one or high-level signal.

- Tables which describe jumper settings show the default position in **bold**, **blue text**.

- Text in *blue italic* indicates a hyperlink within, or external to the document. Click these links to quickly jump to the applicable URL, part, chapter, table, or figure.

- References made to the *phyCARD-Connector* always refer to the high density molex connector on the undersides of the phyCARD-M Single Board Computer.

#### **Abbreviations and Acronyms**

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate unfamiliar terms used in this document.

| Abbreviation | Definition                                         |

|--------------|----------------------------------------------------|

| BSP          | Board Support Package (Software delivered with the |

|              | Development Kit including an operating system      |

|              | (Windows, or Linux) preinstalled on the module and |

|              | Development Tools).                                |

| GPIO         | General purpose input and output.                  |

| GPI  | General purpose input.                                  |  |  |  |  |  |

|------|---------------------------------------------------------|--|--|--|--|--|

| GPO  | General purpose output.                                 |  |  |  |  |  |

| Sx   | User button Sx (e.g. S1, S2, etc.) used in reference to |  |  |  |  |  |

|      | the available user buttons, or DIP-Switches on the      |  |  |  |  |  |

|      | Carrier Board.                                          |  |  |  |  |  |

| Sx_y | Switch y of DIP-Switch Sx; used in reference to the     |  |  |  |  |  |

|      | DIP-Switch on the Carrier Board.                        |  |  |  |  |  |

| СВ   | Carrier Board; used in reference to the phyBASE         |  |  |  |  |  |

|      | Development Kit Carrier Board.                          |  |  |  |  |  |

| DFF  | D flip-flop.                                            |  |  |  |  |  |

| EMB  | External memory bus.                                    |  |  |  |  |  |

| EMI  | Electromagnetic Interference.                           |  |  |  |  |  |

| IRAM | Internal RAM; the internal static RAM on the            |  |  |  |  |  |

|      | Freescale i.MX35 microcontroller.                       |  |  |  |  |  |

| J    | Solder jumper; these types of jumpers require solder    |  |  |  |  |  |

|      | equipment to remove and place.                          |  |  |  |  |  |

| JP   | Solderless jumper; these types of jumpers can be        |  |  |  |  |  |

|      | removed and placed by hand with no special tools.       |  |  |  |  |  |

| PCB  | Printed circuit board.                                  |  |  |  |  |  |

| POR  | Power-on reset                                          |  |  |  |  |  |

| RTC  | Real-time clock.                                        |  |  |  |  |  |

| SMT  | Surface mount technology.                               |  |  |  |  |  |

| SBC  | Single Board Computer; used in reference to the         |  |  |  |  |  |

|      | PCA-A-M1 /phyCARD-A-M1 Single Board                     |  |  |  |  |  |

|      | Computer                                                |  |  |  |  |  |

| VBAT | SBC standby voltage input                               |  |  |  |  |  |

Table 1: Abbreviations and Acronyms used in this Manual

**Note:** The BSP delivered with the phyCARD-M usually includes drivers and/or software for controlling all components such as interfaces, memory, etc.. Therefore programming close to hardware at register level is not necessary in most cases. For this reason, this manual contains no detailed description of the controller's registers, or information relevant for software development. Please refer to the i.MX35 Reference Manual, if such information is needed to connect customer designed applications.

#### **Preface**

As a member of PHYTEC's new phyCARD product family the phyCARD-M is one of a series of PHYTEC Single Board Computers (SBCs) that can be populated with different controllers and, hence, offers various functions and configurations. PHYTEC supports a variety of 8-/16- and 32-bit controllers in two ways:

- (1) as the basis for Rapid Development Kits which serve as a reference and evaluation platform

- (2) as insert-ready, fully functional phyCARD OEM modules, which can be embedded directly into the user's peripheral hardware design.

Implementation of an OEM-able SBC subassembly as the "core" of your embedded design allows you to focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller circuitry. Furthermore, much of the value of the phyCARD module lies in its layout and test.

PHYTEC's new phyCARD product family consists of a series of extremely compact embedded control engines featuring various processing performance classes while using the newly developed X-Arc embedded bus standard. The standardized connector footprint and pin assignment of the X-Arc bus makes this new SBC generation extremely scalable and flexible. This also allows to use the same carrier board to create different applications depending on the required processing power. With this new SBC concept it is possible to design entire embedded product families around vastly different processor performances while optimizing overall system cost. In addition, future advances in processor technology are already considered with this new embedded bus standard making product upgrades very easy. Another major advantage is the forgone risk of potential system hardware redesign steps caused by processor or other critical component discontinuation. Just use one of PHYTEC's other phyCARD SBCs

thereby ensuring an extended product life cycle of your embedded application.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware will further reduce your development time and risk and allow you to focus on your product expertise. Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. With this new innovative full system solution you will be able to bring your new ideas to market in the most timely and cost-efficient manner.

For more information go to:

http://www.phytec.com/services/

## **Ordering Information**

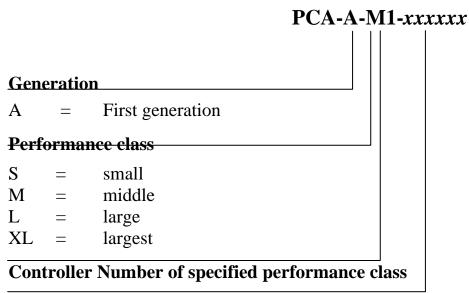

The part numbering of the phyCARD has the following structure:

**Assembly options (depending on model)**

In order to receive product specific information on changes and updates in the best way also in the future, we recommend to register at <a href="http://www.phytec.de/de/support/registrierung.html">http://www.phytec.de/de/support/registrierung.html</a>

You can also get technical support and additional information concerning your product.

The support section of our web site provides product specific information, such as errata sheets, application notes, FAQs, etc.

http://www.phytec.de/de/support/faq/faq-phyCARD-M.html

# **Declaration of Electro Magnetic Conformity of the PHYTEC phyCARD-M**

PHYTEC Single Board Computers (henceforth products) are designed for installation in electrical appliances or as dedicated Evaluation Boards (i.e.: for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### **Caution:**

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

#### 1 Introduction

The phyCARD-M belongs to PHYTEC's phyCARD Single Board Computer module family. The phyCARD SBCs represent the continuous development of PHYTEC Single Board Computer technology. Like its mini-, micro- and nanoMODUL predecessors, the phyCARD boards integrate all core elements of a microcontroller system on a subminiature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware developments.

PHYTEC's phyCARD family introduces the newly developed X-Arc embedded bus standard. Apart from processor performance, a large number of embedded solutions require a corresponding number of standard interfaces. Among these process interfaces are for example Ethernet, USB, UART, SPI, I<sup>2</sup>C, audio, display and camera connectivity. The X-Arc bus exactly meets this requirement. As well the location of the commonly used interfaces as the mechanical specifications are clearly defined. All interface signals of PHYTEC's new X-Arc bus are available on a single, 100-pin, high-density pitch (0.635 mm) connector, allowing the phyCARDs to be plugged like a "big chip" into a target application. The reduced complexity of the phyCARD SBC as well as the smaller number of interface signals greatly simplifies the SBC carrier board design helping you to reduce your time-to-market.

As independent research indicates that approximately 70 % of all EMI (Electro Magnetic Interference) problems stem from insufficient supply voltage grounding of electronic components in high frequency environments approximately 20 % of all pin header connectors on the X-Arc bus are dedicated to Ground. This improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI and EMC guidelines using phyCARD boards even in high noise environments.

phyCARD boards achieve their small size through modern SMD technology and multi-layer design. In accordance with the complexity of the module, 0402-packaged SMD components and laser-drilled microvias are used on the boards, providing phyCARD users with access to this cutting edge miniaturization technology for integration into their own design.

The phyCARD-M is a subminiature (60 x 60 mm) insert-ready Single Board Computer populated with the Freescale i.MX35 microcontroller. Its universal design enables its insertion in a wide range of embedded applications.

Precise specifications for the controller populating the board can be found in the applicable controller Reference Manual or datasheet. The descriptions in this manual are based on the Freescale i.MX35. No description of compatible microcontroller derivative functions is included, as such functions are not relevant for the basic functioning of the phyCARD-M.

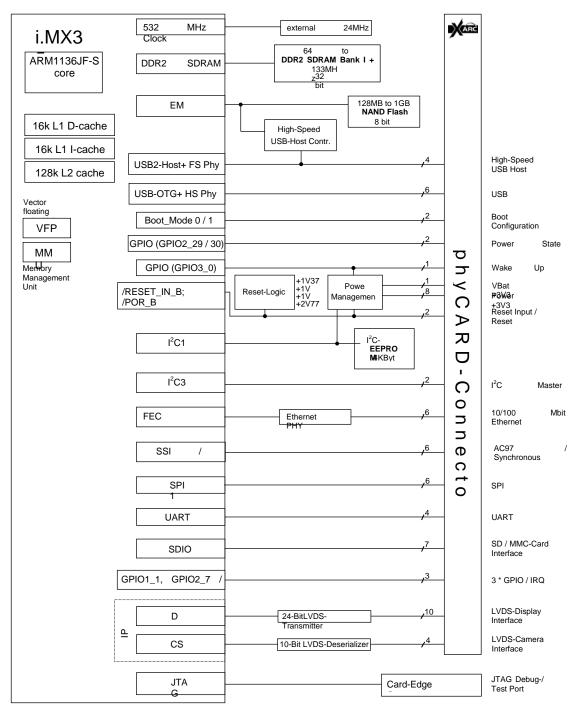

The phyCARD-M offers the following features:

- Subminiature Single Board Computer ( 60 x 60 mm) achieved through modern SMD technology

- Populated with the Freescale i.MX35 microcontroller (BGA400 packaging)

- Improved interference safety achieved through multi-layer PCB technology and dedicated ground pins

- X-Arc bus including commonly used interfaces such as Ethernet, USB, UART, SPI, I<sup>2</sup>C, audio, display and camera connectivity (both LVDS) available at one 100-pin high-density (0.635 mm) Molex connector, enabling the phyCARD-M to be plugged like a "big chip" into target application

- Max. 532 MHz core clock frequency

- Boot from NAND Flash

- 128 MByte (up to 1 GByte) on-board NAND Flash<sup>1</sup>

- 32 MByte (up to 256 MByte) DDR 2 SDRAM on-board

- 4KB (up to 32kB) I<sup>2</sup>C EEPROM

\_

<sup>&</sup>lt;sup>1</sup> Please contact PHYTEC for more information about additional module configurations.

- Serial interface with 4 lines (TTL) allowing simple hardware handshake

- High-Speed USB OTG transceiver

- High-Speed USB HOST transceiver

- Auto HDX/FDX 10/100MBit Ethernet interface, with HP Auto MDI/MDI-X support

- Single supply voltage of 3.3V (max. 600mA) with on-board power management

- All controller required supplies generated on board

- 4 Channel LVDS (18Bit) LCD-Interface

- Support of standard 20 pin debug interface through JTAG connector

- One I<sup>2</sup>C interfaces

- One SPI interfaces

- SD/MMC card interface with DMA

- SSI Interface (AC97)

- Optional LVDS Camera Interface<sup>1</sup>

- 3 GPIO/IRQ ports

- 2 Power State outputs to support applications requiring a power management

- 1 Wake Up input

## 1.1 Block Diagram

Figure 1: Block Diagram of the phyCARD-M

## 1.2 View of the phyCARD-M

Figure 2: Top view of the phyCARD-M (controller side)

Figure 3: Bottom view of the phyCARD-M (connector side)

### 1.3 Minimum Requirements to Operate the phyCARD-M

Basic operation of the phyCARD-M only requires supply of a +3V3 input voltage with 600 mA load and the corresponding GND connection.

These supply pins are located at the phyCARD-Connector X2:

VDD\_3V3\_IN: X2 1A, 2A, 3A, 1B, 2B, 3B

Connect all +3.3V VCC input pins to your power supply and at least the matching number of GND pins.

Corresponding GND: X2 4A, 8A, 13A, 4B, 8B, 13B

Please refer to *section 2* for information on additional GND Pins located at the phyCARD-Connector X2

#### Caution:

We recommend connecting all available +3V3 input pins to the power supply system on a custom carrier board housing the phyCARD-M and at least the matching number of GND pins neighboring the +3V3 pins.

In addition, proper implementation of the phyCARD-M module into a target application also requires connecting all GND pins neighboring signals that are being used in the application circuitry.

Please refer to section 4 for more information.

## **2 Pin Description**

Please note that all module connections are not to exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller manuals/data sheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

As *Figure 4* indicates, all X-Arc bus signals extend to one surface mount technology (SMT) connector (0.635 mm) lining on side of the module (referred to as phyCARD-Connector). This allows the phyCARD-M to be plugged into any target application like a "big chip".

The numbering scheme for the phyCARD-Connector is based on a two dimensional matrix in which column positions are identified by a letter and row position by a number. Pin 1A, for example, is always located in the upper left hand corner of the matrix. The pin numbering values increase moving down on the board. Lettering of the pin connector rows progresses alphabetically from left to right (refer to *Figure 4*).

The numbered matrix can be aligned with the phyCARD-M (viewed from above; phyCARD-Connector pointing down) or with the socket of the corresponding phyCARD Carrier Board/user target circuitry. The upper left-hand corner of the numbered matrix (pin 1A) is thus covered with the corner of the phyCARD-M marked with a triangle. The numbering scheme is always in relation to the PCB as viewed from above, even if all connector contacts extend to the bottom of the module.

The numbering scheme is thus consistent for both the module's phyCARD-Connector as well as the mating connector on the

phyBASE Carrier Board or target hardware, thereby considerably reducing the risk of pin identification errors.

Since the pins are exactly defined according to the numbered matrix previously described, the phyCARD-Connector is usually assigned a single designator for its position (X1 for example). In this manner the phyCARD-Connector comprises a single, logical unit regardless of the fact that it could consist of more than one physical socketed connector.

The following figure illustrates the numbered matrix system. It shows a phyCARD-M with SMT phyCARD-Connectors on its underside (defined as dotted lines) mounted on a Carrier Board. In order to facilitate understanding of the pin assignment scheme, the diagram presents a cross-view of the phyCARD-module showing these phyCARD-Connectors mounted on the underside of the module's PCB.

Figure 4: Pin-out of the phyCARD-Connector (top view, with cross section insert)

Table 2 shows the Pin-out of the X-Arc bus with the functional grouping of the signals, while *Table 3* provides an overview of the Pin-out of the phyCARD-Connector with signal names and descriptions specific to the phyCARD-M. It also provides the appropriate signal level interface voltages listed in the SL (Signal Level) column and the signal direction.

The Freescale i.MX35 is a multi-voltage operated microcontroller and as such special attention should be paid to the interface voltage levels to avoid unintentional damage to the microcontroller and other onboard components. Please refer to the *Freescale i.MX35 Reference Manual* for details on the functions and features of controller signals and port pins.

|           |     |                    |     |     |                       |        | _                     |

|-----------|-----|--------------------|-----|-----|-----------------------|--------|-----------------------|

|           | I/O | Signal             | Pin | Pin | Signal                | I/O    |                       |

| ≥ [       | In  | VCC                | 1A  | 1B  | VCC                   | In     | ) လ                   |

| Supply    | In  | VCC                | 2A  | 2B  | VCC                   | In     | Supply                |

| ر<br>ا    | In  | VCC                | 3A  | 3B  | VCC                   | In     | J <del>≷</del>        |

|           | In  | GND                | 4A  | 4B  | GND                   | In     |                       |

|           | Out | VCC_LOGIC          | 5A  | 5B  | VCC_LOGIC             | Out    |                       |

|           | -   | FEEDBACK           | 6A  | 6B  | VSTBY                 | In     |                       |

|           | In  | nRESET_IN          | 7A  | 7B  | nRESET_OUT            | Out    |                       |

|           | -   | GND                | 8A  | 8B  | GND                   | -      | `                     |

| (         | Out | LVDS_TX0+          | 9A  | 9B  | LVDS_TX1+             | Out    |                       |

|           | Out | LVDS_TX0-          | 10A | 10B | LVDS_TX1-             | Out    | Display               |

| a s       | Out | LVDS_TX2+          | 11A | 11B | LVDS_TX3+             | Out    | ( jaj                 |

| Display   | Out | LVDS_TX2-          | 12A | 12B | LVDS_TX3-             | Out    |                       |

| ä         | -   | GND                | 13A | 13B | GND                   |        | ·                     |

|           | Out | LVDS_TXCLK+        | 14A | 14B | LVDS_CAM_RX+          | In     | Ca                    |

| (         | Out | LVDS_TXCLK-        | 15A | 15B | LVDS_CAM_RX-          | In     | }                     |

| Camera -{ | Out | LVDS_CAM_MCLK      | 16A | 16B | LVDS_CAM_nLOCK        | Out    | ] 🖁                   |

| l²C -{    |     | _ I2C_CLK          | 17A | 17B | I2C_DATA              |        | Camera <sup>2</sup> C |

|           | -   | GND                | 18A | 18B | GND                   | -      |                       |

| Ethernet  | Out | ETH_SPEED          | 19A | 19B | ETH_LINK              | Out    | Ethernet              |

| <u> </u>  | Out | ETH_TX+            | 20A | 20B | ETH_RX+               | In     | } <u>ब</u>            |

|           | Out | ETH_TX-            | 21A | 21B | ETH_RX-               | In     | J ne                  |

| _         | -   | GND                | 22A | 22B | GND                   | -      |                       |

| (         | Out | USB_OTG_PWR1       | 23A | 23B | USB_PWR2              | Out    | ]                     |

| <b>(D</b> | In  | USB_OTG_OC1        | 24A | 24B | USB_OC2               | In     | USB Host              |

| USB OTG   | -   | GND                | 25A | 25B | GND                   | -      |                       |

| ° {       | Bi  | USB_OTG_VBUS1      | 26A | 26B | nSuspend_to_RAM       | Out    |                       |

| S         | Bi  | USB_OTG_D1-        | 27A | 27B | USB_D2-               | Bi     | ]                     |

| ⊃         | Bi  | USB_OTG_D1+        | 28A | 28B | USB_D2+               | Bi     | USB Host              |

| (         | In  | USB_OTG_UID1       | 29A | 29B | nPower_off            | Out    |                       |

| •         | -   | GND                | 30A | 30B | GND                   | -      |                       |

| 9 (       | Bi  | SDIO_D0            | 31A | 31B | SDIO_D1               | Bi     | ) S                   |

| SD/MMC    | Bi  | SDIO_D2            | 32A | 32B | SDIO_D3               | Bi     | SD/MMC                |

| Ö         | Out | SDIO_CLK           | 33A | 33B | SDIO_CMD              | Bi     | ₹                     |

| o, c      | -   | GND                | 34A | 34B | GND                   | _      | <i>J</i> ()           |

| ſ         | Out | SPI CS0            | 35A | 35B | SPI_CS1               | Out    | )                     |

| SP {      | In  | SPI_RDY            | 36A | 36B | SPI_MOSI              | Out    | SP SP                 |

| S         | Out | SPI CLK            | 37A | 37B | SPI_MISO              | In     | _ =                   |

|           | -   | GND                |     | 38B | GND                   | _      | )                     |

| ٢         | Out | UART_TXD           | 39A | 39B | UART_RXD              | In     | ]                     |

| UART {    | In  | UART_RTS           | 40A | 40B | UART_CTS              | Out    | } UART                |

| _         | -   | GND                | 41A | 41B | GND                   | -      | , <u> </u>            |

| AC97/HDA  | Bi  | HDA_SEL/AC97_INT   | 42A | 42B | AC97/HDA_BIT_CLK      | Bi     | AC97/HDA              |

|           | Out | AC97/HDA_SDATA_OUT | 43A | 43B | AC97/HDA_SYNC         | Out    | J 97                  |

| 262       | In  | AC97/HDA_SDATA_IN  | 44A | 44B | AC97/HDA_nRESET       | Out    | 王                     |

| AC        | -   | GND                | 45A | 45B | GND                   | -      | Ä                     |

| ٢         | Bi  | GPIO0/IRQ          | 46A | 46B | SDIO_CD               | In     | } SD/MMC              |

| GPIO      | Bi  | GPIO2/IRQ/PWM      | 47A | 47B | GPIO1/IRQ             | Bi     | - GPIO                |

| Ĺ         | In  | nWKUP              | 48A | 48B | for internal use only | Bi     | , 0, 10               |

|           | -   | GND                | 49A | 49B | GND                   | -<br>- |                       |

| Boot Opt{ | In  | CONFIG0            | 50A | 50B | CONFIG1               | ln     | } Boot Opt.           |

|           |     |                    |     |     |                       |        |                       |

Table 2: X-Arc Bus Pin-out

## Note:

SL is short for Signal Level (V) and is the applicable logic level to interface a given pin.

Those pins marked as "N/A" have a range of applicable values that constitute proper operation.

# Please refer to the phyCARD Design-In Guide (LAN-051) for layout recommendations and example circuitry.

|      | Pin Row X2A    |       |         |                                                                     |  |  |

|------|----------------|-------|---------|---------------------------------------------------------------------|--|--|

| Pin# | Signal         | I/O   | SL      | Description                                                         |  |  |

| 1A   | VDD_3V3_IN     | I     | Power   | 3.3V Primary Voltage Supply Input                                   |  |  |

| 2A   | VDD_3V3_IN     | I     | Power   | 3.3V Primary Voltage Supply Input                                   |  |  |

| 3A   | VDD_3V3_IN     | I     | Power   | 3.3V Primary Voltage Supply Input                                   |  |  |

| 4A   | GND            | -     | -       | Ground 0V                                                           |  |  |

| 5A   | VDD_3V3_IN     | О     | VDD_3V3 | VCC Logic Output                                                    |  |  |

| 6A   | VCC_FEEDBACK   | О     | -       | Feedback Output to indicate the supply voltage required (3V3 or 5V) |  |  |

| 7A   | X_MASTER_RESET | I     | VDD_3V3 | Active low Reset In                                                 |  |  |

| 8A   | GND            | -     | -       | Ground 0V                                                           |  |  |

| 9A   | X_TXOUT0+      | О     | LVDS    | LVDS Chanel 0 positive Output                                       |  |  |

| 10A  | X_TXOUT0-      | О     | LVDS    | LVDS Chanel 0 negative Output                                       |  |  |

| 11A  | X_TXOUT2+      | О     | LVDS    | LVDS Chanel 2 positive Output                                       |  |  |

| 12A  | X_TXOUT2-      | О     | LVDS    | LVDS Chanel 2 negative Output                                       |  |  |

| 13A  | GND            | -     | -       | Ground 0V                                                           |  |  |

| 14A  | X_TXCLKOUT+    | О     | LVDS    | LVDS Clock positive Output                                          |  |  |

| 15A  | X_TXCLKOUT-    | О     | LVDS    | LVDS Clock negative output                                          |  |  |

| 16A  | X_CSI_MCLK     | О     | VDD_3V3 | Clock Output for Camera Interface                                   |  |  |

| 17A  | X_I2C3_SCL     | О     | VDD_3V3 | I2C Clock Output                                                    |  |  |

| 18A  | GND            | =.    | -       | Ground 0V                                                           |  |  |

| 19A  | X_ETH_SPEED    | О     | VDD_3V3 | Ethernet Speed Indicator (Open Drain)                               |  |  |

| 20A  | X_ETH_TX+      | O (I) | ETH     | Transmit positive output (normal) Receive positive input (reversed) |  |  |

| 21A  | X_ETH_TX-      | O (I) | ETH     | Transmit negative output (normal) Receive negative input (reversed) |  |  |

| 22A  | GND            | -     | -       | Ground 0V                                                           |  |  |

| 23A  | X_USBOTG_PWR   | О     | VDD_3V3 | USB-OTG Power switch output open drain                              |  |  |

| 24A  | X_USBOTG_OC    | I     | VDD_3V3 | USB-OTG over current input signal                                   |  |  |

| 25A  | GND            | -     | -       | Ground 0V                                                           |  |  |

| 26A         X_USBPHY1_VBUS         I         5V         USB VBUS Voltage           27A         X_USBPHY1_DM         I/O         USB         USB transceiver cable interface, D-           28A         X_USBPHY1_DP         I/O         USB         USB transceiver cable interface, D+           29A         X_USBPHY1_UID         I         USB on the go transceiver cable ID resistor connection           30A         GND         -         0         Ground 0V           31A         X_SD1_DATA0         I/O         VDD_3V3         SD/MMC Data line both in 1-bit and 4-bit mode           32A         X_SD1_DATA2         I/O         VDD_3V3         SD/MMC Clock for MMC/SD/SDIO           34A         GND         -         Ground 0V           35A         X_CSPI1_SS0         O         VDD_3V3         SPI 1 Chip select 0           36A         X_CSPI1_SPI_RDY         O         VDD_3V3         SPI 1 SPI data ready in Master mode           37A         X_CSPI1_SPLRDY         O         VDD_3V3         SPI 1 clock           38A         GND         -         Ground 0V           39A         X_UART1_TXD         O         VDD_3V3         Serial transmit signal UART 1           40A         X_UART1_RTS         O         VDD_3V3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                 |     |         |                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|---------|-------------------------------------|

| 28A         X_USBPHY1_DP         I/O         USB         USB transceiver cable interface, D+           29A         X_USBPHY1_UID         I         USB on the go transceiver cable ID resistor connection           30A         GND         -         0         Ground 0V           31A         X_SD1_DATA0         I/O         VDD_3V3         SD/MMC Data line both in 1-bit and 4-bit mode           32A         X_SD1_DATA2         I/O         VDD_3V3         SD/MMC Clock for MMC/SD/SDIO           34A         GND         -         -         Ground 0V           35A         X_CSPI1_SS0         O         VDD_3V3         SPI 1 Chip select 0           36A         X_CSPI1_SPI_RDY         O         VDD_3V3         SPI 1 SPI data ready in Master mode           37A         X_CSPI1_SCLK         O         VDD_3V3         SPI 1 clock           38A         GND         -         -         Ground 0V           39A         X_UART1_TXD         O         VDD_3V3         Serial transmit signal UART 1           40A         X_UART1_RTS         O         VDD_3V3         Request to send UART 1           41A         GND         -         -         Ground 0V           42A         X_AC97_INT         I/O         VDD_3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26A | X_USBPHY1_VBUS  | I   | 5V      | USB VBUS Voltage                    |

| 29A   X_USBPHY1_UID   I   USB on the go transceiver cable ID resistor connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27A | X_USBPHY1_DM    | I/O | USB     | USB transceiver cable interface, D- |

| resistor connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28A | X_USBPHY1_DP    | I/O | USB     | USB transceiver cable interface, D+ |

| 31A   X_SD1_DATA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29A | X_USBPHY1_UID   | I   |         |                                     |

| Mode   Mode | 30A | GND             | 1   | 0       | Ground 0V                           |

| mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31A | X_SD1_DATA0     | I/O | VDD_3V3 |                                     |

| 34A GND Ground 0V 35A X_CSPI1_SS0 O VDD_3V3 SPI 1 Chip select 0 36A X_CSPI1_SPL_RDY O VDD_3V3 SPI 1 SPI data ready in Master mode 37A X_CSPI1_SCLK O VDD_3V3 SPI 1 clock 38A GND Ground 0V 39A X_UART1_TXD O VDD_3V3 Serial transmit signal UART 1 40A X_UART1_RTS O VDD_3V3 Request to send UART 1 41A GND Ground 0V 42A X_AC97_INT I/O VDD_3V3 AC97 Interrupt Input 43A X_STXD4 O VDD_3V3 AC97 Transmit Output 44A X_SRXD4 I VDD_3V3 AC97 Receive Input 45A GND Ground 0V 46A X_GPI01_1 I/O VDD_3V3 GPI00 (μC port GPI01_1 at L16) 47A X_GPI02_7 I/O VDD_3V3 GPI00 (μC port GPI02_7 at T7) 48A X_WKUP I VDD_3V3 Wakeup Interrupt Input (μC port GPI03_0 at R4; PMIC port 'Power On 2') 49A GND Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32A | X_SD1_DATA2     | I/O | VDD_3V3 |                                     |

| 35A   X_CSPI1_SSO   O   VDD_3V3   SPI 1 Chip select 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33A | X_SD1_CLK       | 0   | VDD_3V3 | SD/MMC Clock for MMC/SD/SDIO        |

| 36A         X_CSPI1_SPI_RDY         O         VDD_3V3         SPI 1 SPI data ready in Master mode           37A         X_CSPI1_SCLK         O         VDD_3V3         SPI 1 clock           38A         GND         -         Ground 0V           39A         X_UART1_TXD         O         VDD_3V3         Serial transmit signal UART 1           40A         X_UART1_RTS         O         VDD_3V3         Request to send UART 1           41A         GND         -         Ground 0V           42A         X_AC97_INT         I/O         VDD_3V3         AC97 Interrupt Input           43A         X_STXD4         O         VDD_3V3         AC97 Receive Input           45A         GND         -         Ground 0V           46A         X_GPIO1_1         I/O         VDD_3V3         GPIO0 (μC port GPIO1_1 at L16)           47A         X_GPIO2_7         I/O         VDD_3V3         GPIO2 (μC port GPIO2_7 at T7)           48A         X_WKUP         I         VDD_3V3         Wakeup Interrupt Input (μC port GPIO3_0 at R4; PMIC port 'Power On 2')           49A         GND         -         -         Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34A | GND             | 1   | -       | Ground 0V                           |

| 37A X_CSPI1_SCLK O VDD_3V3 SPI 1 clock 38A GND Ground 0V 39A X_UART1_TXD O VDD_3V3 Serial transmit signal UART 1 40A X_UART1_RTS O VDD_3V3 Request to send UART 1 41A GND Ground 0V 42A X_AC97_INT I/O VDD_3V3 AC97 Interrupt Input 43A X_STXD4 O VDD_3V3 AC97 Transmit Output 44A X_SRXD4 I VDD_3V3 AC97 Receive Input 45A GND Ground 0V 46A X_GPI01_1 I/O VDD_3V3 GPI00 (μC port GPI01_1 at L16) 47A X_GPI02_7 I/O VDD_3V3 GPI02 (μC port GPI02_7 at T7) 48A X_WKUP I VDD_3V3 Wakeup Interrupt Input (μC port GPI03_0 at R4; PMIC port 'Power On 2') 49A GND Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35A | X_CSPI1_SS0     | О   | VDD_3V3 | SPI 1 Chip select 0                 |

| 38A GND Ground 0V 39A X_UART1_TXD O VDD_3V3 Serial transmit signal UART 1 40A X_UART1_RTS O VDD_3V3 Request to send UART 1 41A GND Ground 0V 42A X_AC97_INT I/O VDD_3V3 AC97 Interrupt Input 43A X_STXD4 O VDD_3V3 AC97 Transmit Output 44A X_SRXD4 I VDD_3V3 AC97 Receive Input 45A GND Ground 0V 46A X_GPIO1_1 I/O VDD_3V3 GPIO0 (μC port GPIO1_1 at L16) 47A X_GPIO2_7 I/O VDD_3V3 GPIO2 (μC port GPIO2_7 at T7) 48A X_WKUP I VDD_3V3 Wakeup Interrupt Input (μC port GPIO3_0 at R4; PMIC port 'Power On 2') 49A GND Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36A | X_CSPI1_SPI_RDY | О   | VDD_3V3 | SPI 1 SPI data ready in Master mode |

| 39A         X_UART1_TXD         O         VDD_3V3         Serial transmit signal UART 1           40A         X_UART1_RTS         O         VDD_3V3         Request to send UART 1           41A         GND         -         Ground 0V           42A         X_AC97_INT         I/O         VDD_3V3         AC97 Interrupt Input           43A         X_STXD4         O         VDD_3V3         AC97 Transmit Output           44A         X_SRXD4         I         VDD_3V3         AC97 Receive Input           45A         GND         -         Ground 0V           46A         X_GPIO1_1         I/O         VDD_3V3         GPIO0 (μC port GPIO1_1 at L16)           47A         X_GPIO2_7         I/O         VDD_3V3         GPIO2 (μC port GPIO2_7 at T7)           48A         X_WKUP         I         VDD_3V3         Wakeup Interrupt Input (μC port GPIO3_0 at R4; PMIC port 'Power On 2')           49A         GND         -         -         Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37A | X_CSPI1_SCLK    | О   | VDD_3V3 | SPI 1 clock                         |

| 40A X_UART1_RTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38A | GND             | -   | -       | Ground 0V                           |

| 41A GND Ground 0V  42A X_AC97_INT I/O VDD_3V3 AC97 Interrupt Input  43A X_STXD4 O VDD_3V3 AC97 Transmit Output  44A X_SRXD4 I VDD_3V3 AC97 Receive Input  45A GND - Ground 0V  46A X_GPIO1_1 I/O VDD_3V3 GPIO0 (μC port GPIO1_1 at L16)  47A X_GPIO2_7 I/O VDD_3V3 GPIO2 (μC port GPIO2_7 at T7)  48A X_WKUP I VDD_3V3 Wakeup Interrupt Input (μC port GPIO3_0 at R4; PMIC port 'Power On 2')  49A GND - Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39A | X_UART1_TXD     | О   | VDD_3V3 | Serial transmit signal UART 1       |

| 42A         X_AC97_INT         I/O         VDD_3V3         AC97 Interrupt Input           43A         X_STXD4         O         VDD_3V3         AC97 Transmit Output           44A         X_SRXD4         I         VDD_3V3         AC97 Receive Input           45A         GND         -         Ground 0V           46A         X_GPIO1_1         I/O         VDD_3V3         GPIO0 (μC port GPIO1_1 at L16)           47A         X_GPIO2_7         I/O         VDD_3V3         GPIO2 (μC port GPIO2_7 at T7)           48A         X_WKUP         I         VDD_3V3         Wakeup Interrupt Input (μC port GPIO3_0 at R4; PMIC port 'Power On 2')           49A         GND         -         Ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40A | X_UART1_RTS     | О   | VDD_3V3 | Request to send UART 1              |