## Using an External BDM Interface on the phyCORE-MPC555 Development Board (PCM-995 PCB Revision 1174.0)

This application note contains important information regarding the use of external BDM interfaces on the phyCORE-MPC555 Development Board PCM-995 in conjunction with the phyCORE-MCP555 Single Board Computer module.

The factory default jumper settings of the phyCORE-MPC555 Development Board (PCM-995), included in the phyCORE-MPC555 Rapid Development Kit (KPCM-001-xxx), connect the BDM signals from the MPC555 controller through the phyCORE-MPC555 Molex connector to the on-board BDM interface logic. This allows for immediate operation of the Rapid Development Kit and the Metrowerks CodeWarrior tool chain without requiring an external BDM device simply by connecting the DB-25 connector with the LPT port on your computer or laptop.

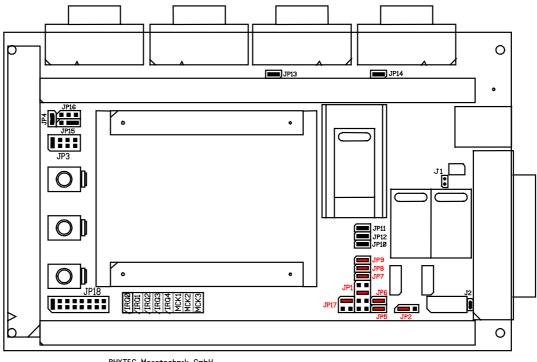

As an alternative, an external BDM interface can be used on the phyCORE-MPC555 Rapid Development Kit at pin header connector X4. In this case Jumpers JP1, JP17 as well as JP5 through JP9 on the Development Board must be removed (*refer to Figure 1, applicable jumpers shown in red color*). This disconnects the controller's BDM signals from the on-board interface logic.

Jumper JP2 must be configured according to the BDM interface supply voltage requirements. Jumper JP2 connects the VBDM signal (pin 9 on X4) with either the +3V3 or the +5V supply voltage of the phyCORE-MPC555 Development Board. No supply voltage is available at pin 9 if Jumper JP2 remains open. Refer to your BDM interface data sheet for more information on the VBDM supply voltage level.

Europe: Support Hotline: +49 (6131) 9221-31 • http://www.phytec.de North America: Support Hotline: +1-800-278-9913 • http://www.phytec.com

LAN-022e\_1 1/3

The pin assignment of the 10-pin header connector X4 on the PHYTEC phyCORE-MPC555 Development Board is shown in the following table. The pinout may differ from the requirements of some BDM interface devices.

| BDM Signal | Pin | Pin | BDM Signal |

|------------|-----|-----|------------|

| VFLS0      | 1   | 2   | /HRESET    |

| GND        | 3   | 4   | DSCK       |

| GND        | 5   | 6   | VFLS1      |

| /HRESIN    | 7   | 8   | DSDI       |

| VBDM       | 9   | 10  | DSDO       |

Table 1: BDM Connector X4 Pin Assignment

A 10 kOhm pull-down resistor for the DSCK signal is located on the phyCORE-MPC555 SBC module.

Some BDM interface devices (for example the Abatron BDI2000) need the /SRESET signal on pin 2 and /HRESET on pin 7. Certain tools drive /HRESET to cause a reset and monitor /SRESET to determine if the part responded and is coming out of reset. /SRESET is available at pin 6C on the three pin header connector X3C. You will have to build a special cable to interface your third-party BDM connection to the phyCORE-MPC555 Development Board.

Refer to section 3.1 of the Development Board PCM-995 Hardware Manual (L-525e.pdf) for more details on the BDM interface and related jumpers.

LAN-022e\_1 2/3

PHYTEC Messtechnik GmbH Basis-MPC555 - 1174.0

Figure 1: Default Jumper Configuration

## Note:

Using an external BDM interface at X4 on the phyCORE-MPC555 Development Board without opening Jumpers JP1, J17 and JP5 through JP9 may result in damage to the on-board circuitry or to the BDM interface. Make sure JP2 is set to the correct position in order to supply the required VBDM voltage. Never operate the hardware with an external BDM interface and the above mentioned jumpers closed!

Europe: Support Hotline: +49 (6131) 9221-31 ● http://www.phytec.de North America: Support Hotline: +1-800-278-9913 ● http://www.phytec.com

LAN-022e\_1 3/3